# Schlussbericht

Zuwendungsempfänger:

Förderkennzeichen:

# Leibniz-Institut für innovative Mikroelektronik - IHP

03X3541 D

Vorhabenbezeichnung:

#### Verbundvorhaben:

Si- und SiGe-Dünnfilme für thermoelektrische Anwendungen (SiGe-TE)

#### Teilvorhaben:

Versetzungsnetzwerk in dünnen SOI-Strukturen für Si-basierte thermoelektrische Generatoren

Laufzeit des Vorhabens:

01.08.2009 bis 28.02.2013

Berichtszeitraum:

01.08.2009 bis 29.02.2013

GEFÖRDERT VOM

im Rahmen der BMBF-Initiative

"Werkstofftechnologien von morgen – Wissenschaftliche Verbundprojekte in den Werkstoff- und Nanotechnologien (WING) "

Die Verantwortung für den Inhalt dieser Veröffentlichung liegt beim Autor.

Schlussbericht gemäß Nr. 8.2 NKBF 98 zum Vorhaben

Verbundprojekt: Si- und SiGe-Dünnfilme

für thermoelektrische Anwendungen (SiGe-TE)

innerhalb der BMBF-Initiative

Werkstofftechnologien von morgen -

Wissenschaftliche Vorprojekte in den Werkstoff- und

Nanotechnologien (WING)

Teilvorhaben 3: Versetzungsnetzwerk in dünnen SOI-Strukturen

für Si-basierte thermoelektrische Generatoren

Förderkennzeichen: 03X3541 D

Laufzeit: 01.08.2009 - 28.02.2013

Leibniz Institut für innovative Mikroelektronik (IHP)

Im Technologiepark 25 15236 Frankfurt (Oder)

Leiter

des Teilprojektes 3: apl. Prof. Dr. Martin Kittler

Tel.: 0335 - 5625 130 Fax: 0335 - 5625 681

E-mail: kittler@ihp-microelectronics.com

Bearbeiter: Dipl.-Phys. Michael Krause

zeitweise an den Arbeiten beteiligt:

Dr. V. Akhmetov Dr. T. Arguirov

Dipl.-Phys. D. Mankovics

Dr. M. Trushin

cand. phys. **B. Schwartz**

2

# **Inhaltsverzeichnis**

| I.   | Kur             | ze Darstellung der Voraussetzungen unter denen das Vorhaben begonnen wurde | . 3 |

|------|-----------------|----------------------------------------------------------------------------|-----|

|      | I.1             | Voraussetzungen                                                            | . 3 |

|      | 1.2             | Aufgaben- und Zielstellung                                                 | . 4 |

|      | 1.3             | Voraussetzungen, unter denen das Vorhaben durchgeführt wurde               | . 4 |

|      | 1.4             | Planung und Ablauf des Vorhabens                                           | . 5 |

|      | 1.5             | Wissenschaftlicher und technischer Stand                                   | . 5 |

|      | 1.6             | Zusammenarbeit mit anderen Stellen                                         | . 9 |

| II.  | Einį            | gehende Darstellung der Vorhabensergebnisse                                | . 9 |

|      | II.1 Er         | zielte Ergebnisse im Einzelnen                                             | . 9 |

|      | II.1.           | 1 AP1 Grundlagen Si-basierter TEG                                          | . 9 |

|      | AP              | 1.1 Einfluss Parameter                                                     | 10  |

|      | AP              | 1.2 Umdotierung                                                            | 25  |

|      | AP              | 1.3 Design der Funktionselemente                                           | 26  |

|      | AP              | 1.4 Herstellung einfacher Teststrukturen                                   | 27  |

|      | AP              | 1.5 Charakterisierung Material und Teststrukturen                          | 30  |

|      | II.1.2          | AP2 Funktionsnachweis Si-basierter thermoelektrischer Generatoren          | 33  |

|      | AP              | 2.1 Herstellung einfacher Funktionselemente                                | 33  |

|      | AP              | 2.2 Charakterisierung der Funktionselemente                                | 38  |

|      | AP              | 2.3 Layout-Simulation                                                      | 41  |

|      | II.1.3 <i>i</i> | AP3 Konzeption eines Demonstrators                                         | 45  |

|      | AP              | 3.1 Integrationskonzept                                                    | 45  |

|      | AP              | 3.2 Entwurf von Bauelementen für thermoelektrische Generatoren (TEG)       | 46  |

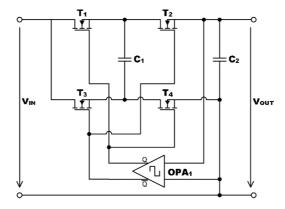

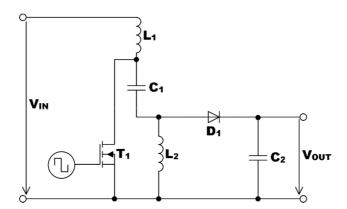

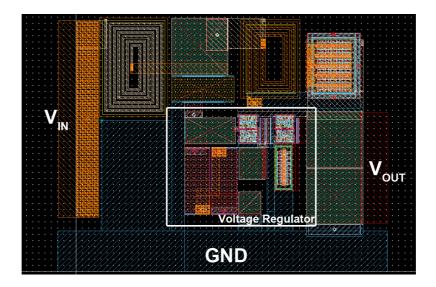

|      | AP              | 3.3 Schaltkreis für Power-Management                                       | 47  |

|      | II.2 Sc         | hutzrechte                                                                 | 49  |

| Ш    | . Ber           | ichte und Workshops                                                        | 50  |

|      | III.1 B         | erichte                                                                    | 50  |

|      | III.2 W         | /orkshops                                                                  | 50  |

| IV   | . Erfo          | olgte und geplante Veröffentlichungen                                      | 51  |

| 1 :4 | oratiu          | norzoichnic .                                                              | 51  |

# I. Kurze Darstellung der Voraussetzungen unter denen das Vorhaben begonnen wurde

# I.1 Voraussetzungen

Das Verbundvorhaben "Si- und Si–Ge-Dünnfilme für thermoelektrischen Anwendungen (Si-Ge-TE)" war auf die Bearbeitung der technologischen Grundlagen zur Realisierung effizienter thermoelektrischer Dünnschichtbauelemente auf Silicium- und Germaniumbasis gerichtet. Im Fokus standen vor allem Konzepte, die den thermoelektrischen Gütefaktor ZT deutlich erhöhen. Die im Projekt bearbeiteten unterschiedlichen Ansätze konzentrierten sich vor allem auf den Temperaturbereich von Raumtemperatur bis etwa 300 °C. Hierfür sollte das Potential der Nanostrukturierung zur Realisierung von Si- bzw. Si–Ge- basierten Dünnschichten gezielt eingesetzt und transferiert werden. Die Herausforderung für die Forschung im Materialsystem Silicium—Germanium besteht darin, sowohl die elektrische als auch die Wärmeleitfähigkeit gezielt und mehr oder weniger unabhängig voneinander einstellen zu können. Solche Möglichkeiten eröffnen sich zum Beispiel mit dem physikalischen Materialdesign unter Verwendung von nanostrukturierten Materialkombinationen wie Supergitter oder Nanosäulen aus Silicium und Germanium mit präziser Kontrolle der Bandstruktur, bzw. dem Einbau von Versetzungsnetzwerken als effektive Phononenstreuer bzw. zur Reduzierung des spezifischen elektrischen Widerstandes.

Das Verbundvorhaben SiGe-TE vereinte die Expertise in den verschiedenen Herstellungsverfahren (Molekularstrahlepitaxie, physikalische Abscheidemethoden, *Waferbonding*), in der Strukturierung (Lithographie, Kontaktierung, Bauelementedesign), in der Bewertung der technologischen Zuverlässigkeit, in der Simulation der physikalischen Parameter und des Bauelementeverhaltens sowie in den verschiedenen physikalischen Messverfahren (Transportmessungen, optische Spektroskopie, Strukturcharakterisierung).

Das Teilvorhaben 3 "Versetzungsnetzwerk in dünnen SOI-Strukturen für Si-basierte thermoelektrische Geratoren" wurde in Kooperation zwischen dem

- Max-Planck-Institut für Mikrostrukturphysik (MPI), Halle,

- Leibnitz-Institut für innovative Mikroelektronik (IHP), Frankfurt (Oder), und der

- Brandenburgischen Technischen Universität, Lehrstuhl Schaltkreisentwurf (BTU),

Cottbus,

durchgeführt. Basierend auf früheren Arbeiten konnte durch die Kooperationspartner gezeigt werden, dass reguläre Versetzungsnetzwerke in direkt gebondeten Si-Wafern interessante physikalische Eigenschaften aufweisen. Versetzungen sind eindimensionale Kristalldefekte und repräsentieren somit natürliche Nanostrukturen. Es konnte zum Beispiel demonstriert werden, dass ein Versetzungsnetzwerk in einer 40 nm dicken SOI-Schicht (SOI: *silicon on insulator*) den spezifischen Widerstand im Vergleich zu einer Referenzschicht ohne Versetzungen dramatisch reduziert. Um das Versetzungsnetzwerk in eine dünne Si-Schicht einzubauen, wurden Schichttransfertechniken (*Waferbonding*) benutzt. Aus der Ohmschen Kennlinie einer npn-Struktur ergab eine einfache Abschätzung einen spezifischen Widerstand von  $\rho_{\text{disl}} \cong 10^{-2}~\Omega\text{cm}$  für eine Probe mit dem Netzwerk, was etwa 3–4 Größenordnungen kleiner als in der Referenzprobe ist. Eine derartig drastische Verringerung des spezifischen Widerstandes würde auch bei Annahme gegenüber dem Kompaktmaterial unveränderter Seebeck-Koeffizienten und thermischer Leitfähigkeit zu einem Anstieg für ZT > 1 führen, was thermoelektrische Anwendungen von dünnen Si-Schichten attraktiv machen würde.

3

## I.2 Aufgaben- und Zielstellung

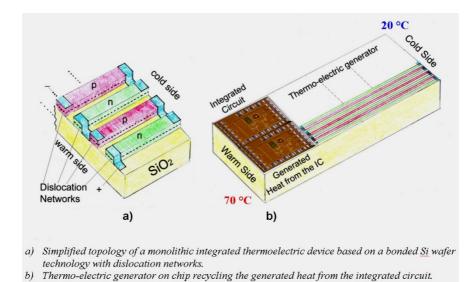

Ziel des Teilvorhabens 3 war es, die Grundlagen neuartiger Si-basierter thermoelektrischer Elemente zu erforschen, deren Funktion nachzuweisen und eine Konzeption für einen Demonstrator, der sich auf einem Chip integrieren lässt, zu erarbeiten. Der neuartige Thermogenerator nutzt die außergewöhnlichen Eigenschaften von Versetzungsnetzwerken in Si aus, die als natürliche Nanostrukturen, eingebettet in das Kristallgitter von Si, anzusehen sind.

Die Konzentration auf dünne Si-Schichten in diesem Teilprojekt bezog sich vor allem auf zukünftige Anwendungen thermoelektrischer Elemente in mikroelektronischen Bauelementen. Während des Betriebes von Schaltkreisen wird elektrische Energie in Abwärme verwandelt, was zur Folge hat, dass sich die Chiptemperatur auf 70-80 °C oder sogar auf noch größere Werte erhöht. Der Verlust von elektrischer Energie reduziert dadurch die Betriebszeit von mobilen Systemen, beispielsweise von Mobiltelefonen oder Laptops. Daher hätte eine Rückwandlung der Abwärme in elektrische Energie - durch Elemente, die auf dem Si-Chip integriert sind und die ein Nachladen der Batterie ermöglichen - große praktische Bedeutung. Anderseits wird durch die Rückgewinnung elektrischer Energie ein entscheidender Beitrag zur Energieeinsparung und Energieeffizienz von elektronischen Systemen erreicht, was wesentlich zur Ressourcenschonung und zum Klimaschutz beiträgt.

Das Teilprojekt 3 konzentrierte sich daher auf Arbeiten zur Anwendung von Versetzungsnetzwerken als natürliche Nanostrukturen, die, ähnlich zu den durch Strukturierungstechniken hergestellten Nanodrähten, die thermoelektrischen Eigenschaften von Si beeinflussen sollten. Auf Grund des durch Vorarbeiten erwiesenen Einfluss eines Versetzungsnetzwerkes in Si auf den Widerstand ( $\rho$ ), und vermutete Einfüsse auf die Wärmeleitung ( $\kappa$ ) sowie möglicherweise auch auf den Seebeck-Koeffizienten (S) gelangt man zu dem Resultat, dass sich durch den Einbau von Versetzungsnetzwerken in dünne Si-Schichten ein ZT-Wert deutlich über 1 erzielen lassen müsste. Das bedeutet, daß der Wirkungsgrad eines thermoelektrischen Generators um einen Faktor von etwa 100 gegenüber einkristallinem Silizium erhöht wird. Dieser Ansatz ist vollkommen neu und erforderte weiterer grundlegender physikalischer Untersuchungen in diesem Projekt.

Hauptziele des Teilprojektes waren deshalb,

- die Grundlagen neuartiger Si-basierter thermoelektrischer Elemente zu erforschen,

- die Funktionsfähigkeit von Si-basierten thermoelektrischen Generatoren (TEG) nachzuweisen und

- eine Konzeption für einen Demonstrator, der sich auf einem Chip integrieren lässt, zu erarbeiten.

#### 1.3 Voraussetzungen, unter denen das Vorhaben durchgeführt wurde

Die Entwicklung innovativer Materialien mit höherer Effizienz ist explizit in Verbindung mit komplett neuen Konzepten der Nanostrukturierung im Rahmen der Fördermaßnahme "Werkstofftechnologien von morgen – Wissenschaftliche Vorprojekte in Werkstoff- und Nanotechnologien" im Rahmen des WING-Programms aufgeführt.

Die Möglichkeit, effiziente Silizium-basierte thermoelektrische Schichten herzustellen, erlaubt eine entscheidende Erweiterung der Basis für den Einsatz thermoelektrischer Bauelemente. Im Lichte aktueller Diskussionen um ressourcenschonende Energietechnologien und einer Verminderung der CO<sub>2</sub>-Emission erlebt die Abwärmenutzung durch geeignete thermoelektrische Bauelemente einen Aufschwung. Darüber hinaus könnten so teure, umweltpolitisch problematische, traditionelle Thermoelektrika auf Schwermetallbasis durch Si und Ge ersetzt werden.

#### I.4 Planung und Ablauf des Vorhabens

Das IHP hat das Vorhaben nach dem vorgegebenen Plan mit einer 6 monatigen Verlängerung erfolgreich durchgeführt. Die Verlängerung war auf Grund einer verspäteten Lieferung von SOI-Wafern erforderlich, die zur Präparation der Funktionselemente benötigt wurden.

#### I.5 Wissenschaftlicher und technischer Stand

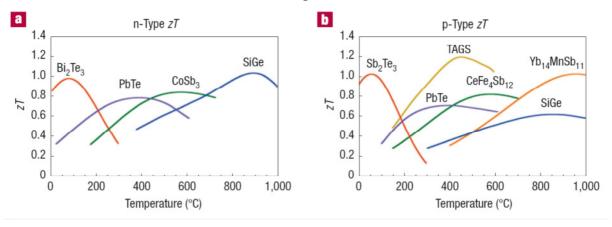

Thermoelektrische Bauteile konvertieren Wärme in Elektroenergie oder umgekehrt. Bei einer wesentlichen Steigerung ihrer gegenwärtigen Effizienz sollten sie ernsthafte Alternativen z. B. für die Nutzung von Abwärme bei der Nutzung fossiler Brennstoffe oder für die Konversion von Sonnenergie in Strom darstellen. Silizium als Basismaterial der Mikroelektronik oder Photovoltaik kann in großer Menge produziert werden. Das notwendige Wissen zur Prozessierung wurde über Jahrzehnte gesammelt. Damit könnte Silizium auch als Basismaterial für die Thermoelektrik in Frage kommen. Bisher ist es aber als Legierung mit Germanium (SiGe) ausschließlich für Hochtemperaturanwendungen interessant (Abbildung 1), etwa in den thermoelektrischen Konvertern von Weltraumsonden.

Die Qualität eines Thermoelektrikums wird allgemein durch den dimensionslosen Gütefaktor

Abbildung 1 Dimensionsloser Gütefaktor ZT von kommerziellen State-of-the-art- Thermoelektrikmaterialien als Funktion der Temperatur T für n-dotierte (a) und p-dotierte Verbindungen (b). Daten nach [1].

ZT beschrieben. ZT hängt vom elektrischen Widerstand  $\rho$ , der thermischen Leitfähigkeit  $\kappa$  und dem Seebeck-Koeffizienten S sowie der Temperatur T ab:

$$ZT = \frac{S^2 \cdot T}{\rho \cdot \kappa} \tag{1}$$

Reines Si ist aufgrund der hohen Wärmeleitfähigkeit  $\kappa$  ein sehr ineffizientes Thermoelektrikum [2]. Die Skalierbarkeit des Elektronen- bzw. Phononentransports führte zur Idee des Bandgap Engineerings bzw. des Quantum Confinements [3] als Schlüssel zur Steigerung von ZT. In dimensionsreduzierten Systemen werden die Energiebänder schmaler. Daraus resultieren höhere effektive Massen und Seebeck-Koeffizienten S. Neben der Beeinflussung der elektrischen Parameter kann die Wärmeleitfähigkeit mit einer erhöhten Phononenstreuung

an Grenzflächen von multiphasigen Kompositen oder Dünnfilm-Supergittern verringert werden. Nach der theoretischen Vorhersage und ersten bestätigenden Messungen bleibt aber die Realisierung eines entsprechenden thermoelektrischen Bauelementes mit hohem Gütefaktor noch offen.

Für die Anwendung dimensionsreduzierter Systeme werden unterschiedliche Ansätze verfolgt: (i.) Entwicklungen von thermoelektrischen Dünnschichten bzw. Supergittern existieren seit etwa 15 Jahren. Ausgehend von grundlegenden Überlegungen zu den thermoelektrischen Eigenschaften von Supergittern [4], gelang es in der Folge, einen hohen ZT-Wert in verschiedenen Materialien nachzuweisen. Der Vorteil der Abscheidung von dünnen Filmen ist, dass Schichten mit gewünschten Eigenschaften maßgeschneidert werden können [5]. Der Transport kann bei Vielfachschichten entweder parallel zum Schichtstapel oder senkrecht dazu erfolgen. Im ersten Fall können bei sehr dünnen Schichten Quanteneffekte den Elektronentransport beeinflussen. Allerdings ist zu erwarten, dass die thermoelektrischen Eigenschaften nur geringfügig verbessert werden, da sich die Phononen innerhalb der Schichten ungestört ausbreiten können, wenn nicht zusätzliche Maßnahmen ergriffen werden. Beim Transport senkrecht zum Filmstapel kann ein nahezu ungestörter Transport von Elektronen und Löchern erreicht werden. Die Grenzflächen wirken als Phononenbarrieren. Der Anstieg im Gütefaktor resultiert im Wesentlichen aus der Reduzierung der Wärmeleitung im Supergitter. Für Quantenpunkt-Supergitter, wie z. B. Ge/Si, werden ebenfalls deutliche Anstiege in ZT erwartet [6] und durch erste Ergebnisse bestätigt [7]. In Supergittern aus degenerierten Halbleitern spielt darüber hinaus der nichtlineare Transport (thermionische Emission) eine bedeutsame Rolle für eine ZT-Steigerung.

- (ii.) Neuere Untersuchungen zeigen, dass Si-Nanodrähte sehr gute thermoelektrische Eigenschaften aufweisen. ZT-Werte von 0.6 [8] bzw. 0.4 [9] konnten nahe Raumtemperatur erreicht werden. Boukai et al. [8] verwendeten "Si-Drähte" mit etwa rechtwinkligem Querschnitt (10-20 nm) und Hochbaum et al. [9] nutzten "Si-Drähte" mit etwa kreisförmigem Querschnitt (20-300 nm), die raue Oberflächen aufwiesen. Die beobachtete Erhöhung des ZT-Wertes von Si um nahezu 2 Größenordnungen (von 0.01 auf beinahe 1) wurde von den Autoren hauptsächlich auf eine starke Reduzierung der Wärmeleitfähigkeit  $\kappa$  in den Si-Nanodrähten zurück geführt. Es wurde berichtet, dass dieser sog. "phonon drag" abhängt von der Form der Si-Nanodrähte sowie von Hindernissen, die den Wärmefluss eindämmen, wie der Oberflächenrauhigkeit der Drähte [9].

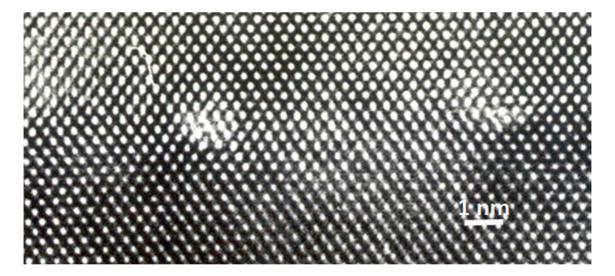

- (iii.) Neben den durch unterschiedliche Strukturierungsmethoden erzeugten Si-Nanodrähten [8, 9] wurden von den Kooperationspartnern in diesem Teilprojekt in den zurückliegenden Jahren Versetzungen in Si untersucht. Versetzungen sind eindimensionale Kristalldefekte mit Längen von mehreren Mikrometern und Durchmessern von ca. 1 nm (Abbildung 2). Auf Grund dieser Dimensionen können Versetzungen als natürliche Nanostrukturen angesehen werden, die in einer perfekten Si-Matrix eingebettet sind. Definierte, 2-dimensionale Anordnungen von Versetzungen (Versetzungsnetzwerke) können mittels dem sog. Waferbonden reproduzierbar hergestellt werden [10, 11].

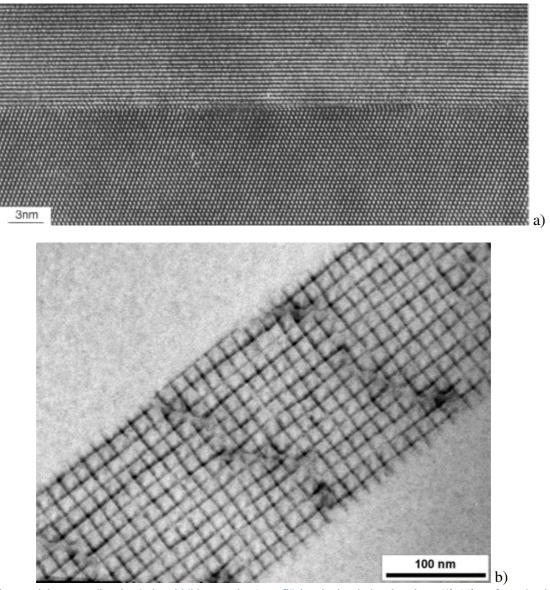

Abbildung 2 Elektronenmikroskopische Abbildung (HREM) von Versetzungen in Si (gebondete Grenzfläche). Dargestellt sind Querschnitte durch Stufen- (60°-) Versetzungen, die durch eine eingeschobene Netzebene charakterisiert sind.

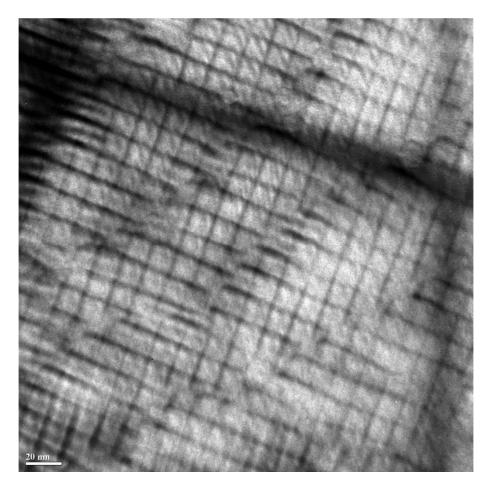

Regelmässige Versetzungsnetzwerke, die durch Waferbonden von Si-Wafern erzeugt werden, weisen eine Reihe aussergewöhnlicher physikalischer Eigenschaften auf [12, 13]. Eine typische TEM-Aufnahme eines solchen Netzwerkes ist in Abbildung 3 gezeigt. Die Entstehung und Struktur der Netzwerke wird in [10, 11]

Abbildung 3 Elektronenmikroskopische Abbildung eines Versetzungsnetzwerkes in der Grenzfläche eines gebondeten Waferpaares (Si(100). Schraubenversetzungen (hervorgerufen durch die twist-Komponente der Fehlorientierung) bilden ein Netzwerk mit quadratischen Maschen, das von Stufenversetzungen (60°-Versetzungen), die durch die tilt-Komponente der Fehlorientierung hervorgerufen werden, überlagert wird.

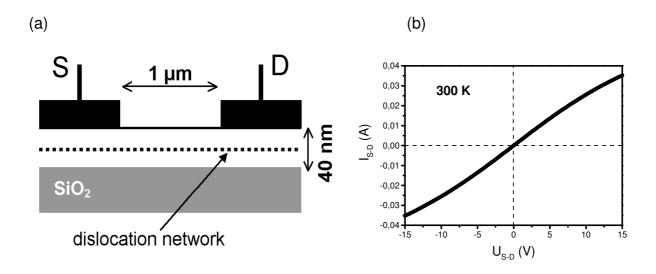

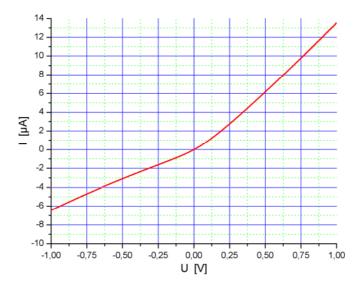

beschrieben. Die Netzwerke in Si beeinflussen u.a. den Transport von Minoritäts- und von Majoritäts-Ladungsträgern und damit den elektrischen Widerstand dramatisch. Ein Versetzungsnetzwerk, das in der Mitte einer ca. 40 nm dicken SOI-Schicht gelegen ist, reduziert den spezifischen Widerstand  $\rho$  im Vergleich zur Referenzprobe ohne Netzwerk, um etwa 4 Größenordnungen [14]. Die Probenstruktur ist in Abbildung 4a schematisch dargestellt. Die p-leitende SOI-Schicht wurde mit Ohm'schen Kontakten versehen, die im Abstand von 1 µm aufgebracht wurden. In Abbildung 4b ist die bei Raumtemperatur gemessene IU-Kennlinie gezeigt, die Ohm'schen Charakter aufweist. Der Widerstand dieser Struktur mit Netzwerk beträgt  $R_{\text{NW}} \sim 4 \times 10^2~\Omega$ . Dagegen hatte die Referenzprobe ohne Netzwerk einen Widerstand von  $R_{\text{Ref}} \sim 2 \times 10^6~\Omega$ . Eine grobe Abschätzung liefert für den spezifischen Widerstand der SOI-Schicht mit Netzwerk  $\rho_{\text{NW}} < 10^{-2}~\Omega$ cm, während die Referenzprobe  $\rho_{\text{Ref}} > 20~\Omega$ cm aufweist. Auch andere Autoren haben ähnliche Beobachtungen publiziert, d.h. eine Widerstands-Reduzierung durch ein Versetzungsnetzwerk in Si [15].

Die physikalischen Ursachen dieser extremen Veränderung der Transporteigenschaften der

Abbildung 4 Schematische Darstellung der Probe (npn-Struktur) mit einer 40 nm dicken Si-Schicht (SOI-Struktur), die ein Versetzungsnetzwerk enthält (a). I-U-Charakteristik der Probe bei 300 k mit Ohmschem Charakter. Die Referenzprobe ohne Netzwerk weist einen um etwa 10<sup>4</sup> höheren Widerstand auf (b).

Ladungsträger durch die Versetzungen sind noch nicht endgültig verstanden. Als Ursache wird ballistischer Transport vermutet, siehe z.B. [16, 17].

Weiterhin kann davon ausgegangen werden, dass durch Versetzungen auch die thermische Leitfähigkeit  $\kappa$  und der Seebeck-Koeffizient S des Siliziums beeinflußt werden. Analog zu den Si-Nanodrähten [8, 9] verursachen Versetzungsnetzwerke eine zusätzliche Phononen-Streuung, durch die  $\kappa$  reduziert wird. In der älteren Literatur sind Hinweise darauf zu finden, dass der Seebeck-Koeffizient S in polykristallinem, d.h. in Si das Kristalldefekte enthält, etwa um den Faktor 2 größer ist, als im einkristallinen Si [18].

Fasst man den erwiesenen Einfluss der Versetzungsnetzwerke in Si auf den Widerstand ( $\rho$ ), und die vermuteten Einfüsse auf die Wärmeleitung ( $\kappa$ ) und möglicherweise auch auf den Seebeck-Koeffizienten (S) zusammen, gelangt man unter Hinzuziehung von Gl. (1) zu dem Resultat, dass sich durch den Einbau von Versetzungsnetzwerken in Si-Nanostäbe ZT-Werte deutlich über 1 erzielen lassen müssten. Das bedeutet, daß der Wirkungsgrad eines thermoelektrischen Generators entsprechend

$$\eta_{TEG} = \eta_{Carnot} \times \frac{\sqrt{1 + ZT} - 1}{\sqrt{1 + ZT} + \frac{T_{kalt}}{T}}$$

(2)

um einen Faktor von etwa 100 gegenüber einkristallinem Silizium erhöht. Dieser Ansatz ist unserem Wissen nach vollkommen neu.

#### I.6 Zusammenarbeit mit anderen Stellen

Das Verbundprojekt erforderte eine enge Abstimmung und Zusammenarbeit mit den Partnern in den anderen Teilprojekten, insbesondere der MLU Halle (Teilprojekt 4) zur thermoelektrischen Charakterisierung und dem Fraunhofer-Institut für Werkstoffmechanik, Halle (Teilprojekt 5) zu Aufbau- und Verbindungstechniken.

Am IHP werden seit langer Zeit die Eigenschaften von ausgedehnten Kristalldefekten in Si untersucht. Neben dem Defekt-Engineering, z.B. für die Photovoltaik, steht dabei die Nutzbarkeit von Kristalldefekten als aktive Komponenten von Bauelementen im Fokus, z.B. für Photonik oder Thermoelektrizität. Zu den genannten Themen betreibt das IHP eine Zusammenarbeit u.a. mit dem HZB Berlin, der TU Berlin, den Universitäten Göttingen, Stuttgart und St. Petersburg.

Im MPI für Mikrostrukturphysik, Halle, werden unterschiedliche Ansätze zu Si-basierten Thermoelektrika verfolgt. Hierzu zählen vor allem Untersuchungen zu den thermoelektrischen Eigenschaften von porösem Si [19] als auch von Si- und SiGe-Nanodrähten [20]. Umfassende Ergebnisse dieser Arbeiten wurden in Dissertationen dargestellt. Arbeiten zur Entstehung und den Eigenschaften von Versetzungen in den Grenzflächen gebondeter Wafer wurden intensiv über einen längeren Zeitraum mit der Duke University, Durham, NC, durchgeführt. Weitere Untersuchungen hierzu erfolgen auch in Kooperation mit zahlreichen anderen Partnern, wie z.B. dem Fraunhofer-Institut für Solare Energiesysteme, Freiburg.

Die BTU, Lehrstuhl für Schaltkreisentwurf, befasst sich mit schaltungstechnischen Problemen neuer Technologien. Auf der Basis der zur Verfügung stehender Technologien werden neue Bauelemente wie z.B. Thermoelemente, passive Hochfrequenz-Strukturen etc. entwickelt und in Schaltungen eingesetzt. Der Lehrstuhl hält enge Beziehungen zur Industrie (INFINEON), TU Berlin, TU Wien, Institut für Halbleiter Physik (Akademie der Wissenschaften Kiew) und anderen Partnern.

# II. Eingehende Darstellung der Vorhabensergebnisse

#### II.1 Erzielte Ergebnisse im Einzelnen

Die im Teilvorhaben durchgeführten Arbeiten umfassten die drei Arbeitspakte AP1 bis AP3 sowie ein Arbeitspaket 4 über Berichte und Workshops. Diese sind detailliert untersetzt, wie unten erläutert wird, und den drei beteiligten Gruppen - BTU Cottbus, MPI Halle und IHP Frankfurt (Oder) - inhaltlich zugeordnet.

#### II.1.1 AP1 Grundlagen Si-basierter TEG

Die Arbeiten im AP 1 wurden vom IHP Frankfurt (Oder) koordiniert.

#### **AP 1.1 Einfluss Parameter**

Vor Beginn der Projektarbeiten lagen nur Daten zur Auswirkung eines Netzwerkes mit einer bestimmten Struktur auf den Widerstand, in einer 40 nm dicken SOI-Schicht aus p-Si (siehe Kapitel I.5). Im Rahmen dieses Projektes sollte jedoch ein viel breiteres Parameterfeld untersucht werden. Um die optimalen Bedingungen für Si-basierte TEG finden zu können, müssen Informationen zumindest über den Einfluss folgender Parameter gewonnen werden: Struktur des Netzwerkes, Dicke der SOI-Schicht und Tiefenposition des Netzwerkes darin, Dotierstoffkonzentration und Leitungstyp. Dabei mußte geklärt werden, in welcher Weise diese Parameter die wichtigen ZT bestimmenden Größen beeinflussen. Dazu ist auch das Verständnis der physikalischen Ursachen der Einwirkung von Versetzungen auf den elektrischen Widerstand und die thermische Leitfähigkeit notwendig.

Auf Grund des Fehlens der amorphen SiO<sub>2</sub>-Schichten in den Grenzflächen sind hydrophob gebondete Grenzflächen durch den direkten (atomaren) Kontakt der Oberflächen beider Wafer charakterisiert (Abbildung 5a). Im Idealfall, d.h. bei Verwendung gleicher Materialien und bei exakt gleicher Kristallorientierung, würde die Grenzfläche aus energetischen Gründen aufgelöst werden.

Abbildung 5 Elektronenmikroskopische Abbildungen der Grenzflächen hydrophob gebondeter Si(100)-Wafer. Die Abb. (a) zeigt die hochauflösungselektronenmikroskopische (HREM) Querschnittsabbildung [21]. In den Grenzflächen kommt

es auf Grund der Fehlorientierung beider Kristallgitter zur Ausbildung von Versetzungen (b). Elektronenmikroskopische Abbildung an einem Schrägschnitt (25°).

Das Resultat wäre ein Einkristall. Da es praktisch jedoch unmöglich ist, zwei atomar glatte Wafer mit exakt der gleichen Kristallorientierung zu realisieren bzw. zu bonden, existieren Fehlorientierungen zwischen den Kristallgittern beider Wafer. Die Anpassung beider Kristallgitter erfolgt dann während des Bondprozesses durch die Bildung von Kristalldefekten (Versetzungen) in der Grenzfläche. Da durch den Prozeß Wafer mit Durchmessern bis zu 300 mm miteinander verbunden werden, entstehen ausgedehnte planare Netzwerke solcher Versetzungen (Abbildung 5b). Sowohl der Versetzungstyp, als auch die Anordnung der Versetzungen, werden durch die Kristallorientierung und die Art (planar, azimutal), sowie den Grad der Fehlpassung beeinflußt. Im Fall des Bondens von (100)-orientierten Si-Wafern entsteht zum Beispiel ein quadratisches Netzwerk von Schraubenversetzungen als Folge der planaren Fehlpassung, das von 60°-Versetzungen (infolge der azimutalen Fehlorientierung) überlagert wird (Abbildung 5b).

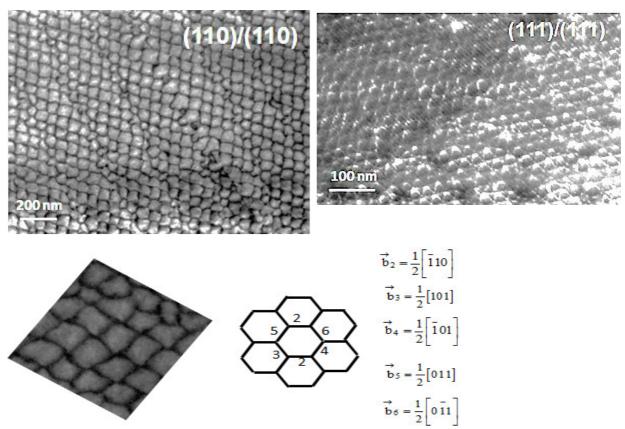

Die Struktur der in den Grenzflächen gebondeter Wafer auftretenden planaren Versetzungsnetzwerke und auch die Typen dieser die Netzwerke bildenden Versetzungen hängen von zahlreichen Faktoren ab. Entscheidend ist in erster Linie die Kristallorientierung beider Wafer. Wie die Abbildung 5 zeigt, sind Versetzungsnetzwerke aus Schraubenversetzungen für gebondete Si(100)-Wafer typisch. Durch diese Versetzungen wird die auf Grund der Verdrehung beider Kristallgitter in der Ebene (rotational misfit) auftretende Fehlpassung kompensiert. Dieses Versetzungsnetzwerk wird von 60°-Versetzungen überlagert, die die dazu senkrechte Fehlpassung (azimutal misfit) kompensieren. Ändern sich die Kristallorientierungen beider Wafer, so ändert sich auch das in der Grenzfläche erzeugte Versetzungsnetzwerk. Die Abbildung 6 zeigt zum Beispiel Versetzungsnetzwerke, die durch das Bonden von Wafern mit (110)- bzw. (111)-Orientierungen erhalten werden. Im Gegensatz zum Bonden (100)orientierter Wafer werden so etwa bei Verwendung von (111)-orientierten Wafern Netzwerke aus Shockley'schen Partialversetzungen mit Burgers-Vektoren des Typs  $\mathbf{b}$  = a/6<112> gebildet. Einen Aussschnitt aus dem Versetzungsnetzwerk in der Grenzfläche von (110)/(110)gebondeten Wafern zeigt der untere Teil der Abbildung 6. Das Netzwerk mit hexagonaler Maschenstruktur wird aus Schraubenversetzungen mit Burgers-Vektoren des Typs b = a/2<110> aufgebaut und beschreibt die Drehwinkelkorngrenze (twist boundary). Es treten aber auch Wechselwirkungen mit den 60°-Versetzungen (hervorgerufen durch die tilt-Komponente) auf, die zum Teil die hexagonale Maschenstruktur modifizieren können. Nach Goodhew u.a. [22] besteht die ursprüngliche (110)-Drehwinkelkorngrenze aus einem Satz von Schraubenversetzungen des Typs  $\mathbf{b} = a/2 \begin{vmatrix} 1 & 1 \\ 1 & 1 \end{vmatrix}$  in der Ebene, sowie einem dazu senkrechten Satz von Schraubenversetzungen des Typs  $\mathbf{b}$  = [001]. Letztere sind jedoch instabil

$$[001] \rightarrow 1/2[101] + 1/2 \begin{bmatrix} 1 & 0 & 1 \\ 1 & 0 & 1 \end{bmatrix} . \tag{3}$$

Die Wechselwirkung dieser durch die Dissoziation entstandenen Versetzungen mit den ursprünglichen, horizontalen Schraubenversetzungen führt zu

$$1/2[101]+1/2[110] \rightarrow 1/2[011]$$

(4a)

und

und dissoziieren entsprechend der Gleichung

$$1/2 \begin{bmatrix} \bar{1}01 \end{bmatrix} - 1/2 \begin{bmatrix} \bar{1}10 \end{bmatrix} \rightarrow 1/2 \begin{bmatrix} \bar{0}11 \end{bmatrix}$$

(4b)

Abbildung 6 Transmissionselektronenmikroskopische Abbildung der Versetzungsstrukturen in den Grenzflächen gebondeter Wafer mit unterschiedlichen Oberflächenorientierungen der Ausgangswafer (oben). Die Orientierungen sind in den Abbildungen angegeben. Der untere Teil der Abbildung zeigt einen Ausschnitt aus dem Versetzungsnetzwerk des (110)/(110)-gebondeten Waferpaares und die schematische Darstellung der Versetzungsstruktur. Die Ziffern kennzeichnen die entsprechenden Burgers-Vektoren. Nach dem Bonden wurden die Waferpaare bei 1000°C getempert.

Umordnungen der verschiedenen Segmente führen dann zu einer relaxierten Anordnung, wie sie schematisch im unteren Teil der Abbildung 6 dargestellt ist. Alle Segmente liegen hierbei parallel zu {111}-Ebenen.

Da für den Bondprozeß Wafer mit allen denkbaren Kristallorientierungen verwendet werden können, ist die Ausbildung einer Vielzahl von Versetzungsnetzwerken möglich. Bourdelle u.a. [23] berichten zum Beispiel über die Struktur der Versetzungen in der Grenzfläche von sog. hybrid-orientierten Wafern, wobei ein (110)-orientierter mit einem (100)-orientierten Wafer verbunden wird. Unter der Orientierungsbedingung <110>{110} parallel zu <110>{100} werden nur durch die Verkippung beider Wafer hervorgerufene parallele Anordnungen von (vermutlich) 60°-Versetzungen beobachtet. Demgegenüber ergaben Untersuchungen von Toyoda u.a. [24] für das Bonden gleicher Waferpaare, jedoch mit der Orientierungsbeziehung <100>{110} parallel zu <110>{100} Hinweise auf planare Anordnungen von Defekten, deren Burgersvektor etwa einem Viertel dessen einer Schraubenversetzung entsprechen würde.

Weitere Modifizierungen der Versetzungsnetzwerke in den Grenzflächen der hydrophob gebondeten Wafer lassen sich durch eine Variation der Dreh-(twist angle) und Kippwinkel (tilt angle) erreichen. Insbesondere für solche Fälle, in denen beide Winkel nahezu gleich sind, treten ausgeprägte Wechselwirkungen zwischen den unterschiedlichen Versetzungsty-

pen auf, die zu komplexen Netzwerkstrukturen führen. Ein weiterer Faktor, der die Morphologie der Versetzungsnetzwerke beeinflußt, ist die Temperatur der Wärmebehandlung, durch die zusätzliche Versetzungsreaktionen, wie Gleiten oder Klettern, ermöglicht werden und damit weiterhin zur Komplexität der Versetzungsnetzwerke beitragen.

Die Darstellung zeigt, dass sowohl die Morphologie der erzeugten Versetzungsnetzwerke, als auch die diese Netzwerke bildenden Typen von Versetzungen durch zahlreiche Faktoren beeinflußt werden können. Eigene, als auch nach Kenntnis der Autoren in der Literatur beschriebene Untersuchungen konzentrieren sich deshalb auf Netzwerke, die durch das hydrophobe Bonden von (100)-orientierten Wafern erhalten werden. Desweiteren wurden in nahezu allen beschriebenen Fällen Versetzungsnetzwerke mit kleinen Dreh- $(\vartheta_{twist})$  und Kippwinkeln  $(\vartheta_{tilt})$  von  $\vartheta_{twist} \neq \vartheta_{tilt} < 5^\circ$  betrachtet, so dass Netzwerke resultieren, die allgemein als Kleinwinkelkorngrenzen bezeichnet werden [25]. Entsprechend der *Coincidence Lattice Theory* [26] sind diese  $\Sigma$ 1-Korngrenzen.

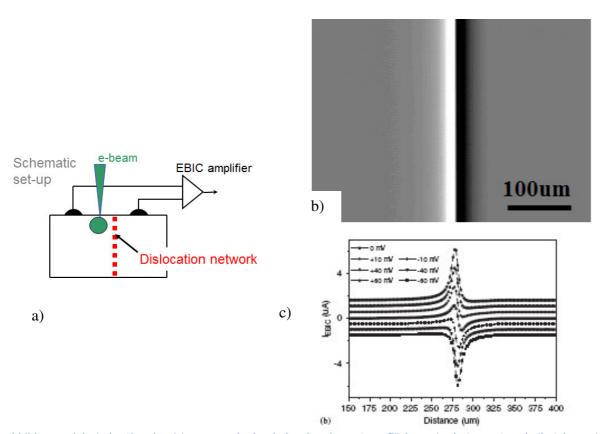

Zur Messung der elektrischen Aktivität von Defekten wurden in der Literatur zahlreiche Untersuchungstechniken eingesetzt, wie Hall-Effekt-Messungen, EPR-Spektroskopie (electron paramagnetic resonance spectroscopy), DLTS- (deep level transient spectroscopy) und EBIC-Techniken (electron beam induced current). Hall-Effekt-Messungen und EPR-Spektroskopie fanden vor allem für Untersuchungen an deformiertem Silizium Anwendung, während DLTS-und EBIC-Techniken auch zur Analyse weniger Defekte oder einzelner Korngrenzen in polykristallinem Si eingesetzt wurden. Für die hier beschriebenen Untersuchungen fanden vor allem EBIC- und DLTS-Techniken Anwendung.

Zur Messung der Potentialbarrieren an den Grenzflächen gebondeter Wafer wurde die sog. Korngrenzen-EBIC-Technik (GB-EBIC, grain boundary EBIC [27]) verwendet. Die schematische Darstellung des Verfahrens zeigt die Abbildung 7a. Hierzu wird ein Querschnitt der Probe angefertigt und nach Herstellung der Kontakte im Rasterelektronenmikroskop mittels EBIC-Technik (electron beam induced current) untersucht. Ein Beispiel der Analyse einer gebondeten Grenzfläche zeigt die Abbildung 7b. Die dargestellte Grenzfläche, die durch hydrophobes Bonden zweier p-leitender Wafer entstand, enthält ein Versetzungsnetzwerk, dessen Fehlorientierung mittels Transmissionselektronenmikroskopie mit  $\vartheta_{twist}$  = 0,73° und  $\vartheta_{tilt}$  = 0,05° bestimmt wurde [12]. Messungen der EBIC-Kontrastprofile der dargestellten Grenzfläche zeigt die Abbildung 7c. Aus einer Vielzahl von Messungen, die im Rahmen des Projektes erfolgten, resultiert, dass die präparierten Grenzflächen durch Potentialbarrieren von weniger als 100 meV charakterisiert sind. Im Vergleich mit den Literaturwerten [28] sind die Potentialbarrieren um mehr als den Faktor zwei geringer. Weitere Messungen der Temperaturabhängigkeit des EBIC-Kontrastes weisen darauf hin, dass die Dichte tiefer Störstellen etwa 10<sup>5</sup> pro Zentimeter entlang den Versetzungslinien im Netzwerk ist [29]. Wird die Si-Gitterkonstante a<sub>0</sub> = 0,543 nm für den Abstand zweier Atome entlang der Versetzungslinie angenommen, so folgt daraus eine Anzahl von etwa 5·10<sup>8</sup> Si-Atomen pro Zentimeter Versetzungslänge, was bezüglich der Dichte der Störstellen bedeutet, dass ca. jedes tausendste Si-Atom in der Versetzungslinie mit einer Störstelle behaftet ist.

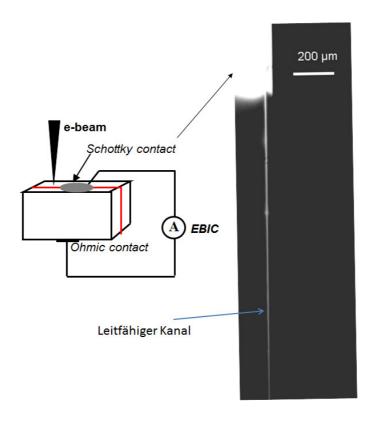

Werden Querschnitte von hydrophob gebondeten Wafern an einer Seite mit einem Schottky-Kontakt versehen, so erscheint die gebondete Grenzfläche als heller Kontrast in der EBIC-Abbildung (Abbildung 8). Der vom Schottky-Kontakt ausgehende helle Kontrast ist über große Distanzen (mehrere Millimeter) sichtbar und wird durch den Transport von Minoritätsladungsträgern entlang der Grenzfläche zur sammelnden Schottky-Barriere hervorgerufen [30]. Der Transport von Ladungsträgern über große Distanzen ist ein Anzeichen dafür, dass

Abbildung 7 Elektrische Charakterisierung von hydrophob gebondeten Grenzflächen mittels GB-EBIC-Technik. Schematische Darstellung des Meßverfahrens (a) und EBIC-Abbildung ohne Vorspannung (zero bias) (b). Gemessene EBIC-Kontrastprofile für unterschiedliche Vorspannungen (c) für die in Abb. (b) gezeigte Grenzfläche.

Versetzungen extrem leitfähige Kanäle für Ladungsträger darstellen. In dem hier betrachteten Fall werden Minoritätsladungsträger über die Versetzungen transportiert. Durch die Untersuchungen konnte desweiteren gezeigt werden, dass auch ein bevorzugter Transport von Majoritätsladungsträgern über die Versetzungen in den Grenzflächen gebondeter Wafer existiert (vergl. Abbildung 4b).

Die DLTS-Technik (deep level transient spectroscopy) wird häufig auch zur Charakterisierung der elektronischen Struktur von Versetzungen herangezogen. Während aus den Analysen deformationsinduzierter Versetzungen zahlreiche Ergebnisse bekannt sind, ist diese Methode bisher kaum zur Beschreibung der elektronischen Struktur von Versetzungen in gebondeten Grenzflächen herangezogen worden. Eine Ursache ist sicher die, dass durch den Waferbondprozeß die Versetzungsnetzwerke tief unterhalb der Oberfläche gebildet werden. Erst in letzter Zeit wurden durch den Waferbondprozeß unter Einbeziehung von SOI-Wafern mit dünnen Si-Schichten die Möglichkeiten geschaffen, die Versetzungsnetzwerke so nahe an der Oberfläche zu erzeugen, dass der Einsatz der DLTS-Technik sinnvoll wird. Ergebnisse von DLTS-Untersuchungen sind bisher nur von einigen Versetzungsnetzwerken bekannt, die unter spezifischen Bedingungen, d.h. Bonden unter hydrophilen Bedingungen und Ausdiffusion des Sauerstoffs bei sehr hohen Temperaturen (T = 1200°C) für 2 Stunden, realisiert wurden

Abbildung 8 Bildung eines leitfähigen Kanals entlang der gebondeten Grenzfläche. Der linke Teil der Abbildung zeigt schematisch die Meßanordnung, der rechte Teil die EBIC-Abbildung.

[31]. Die Untersuchungen wiesen die Existenz von Haftstellen (shallow traps) und tiefen Zuständen (deep states) nach. Die Konzentrationen beider Störstellen sind abhängig vom Drehwinkel (twist) des Versetzungsnetzwerkes. Für Versetzungsnetzwerke mit  $\vartheta_{\text{twist}} \leq 3^{\circ}$  dominieren shallow traps, während für  $\vartheta_{\text{twist}} \geq 3^{\circ}$  tiefe Störstellen dominieren.

Die Erzeugung von definierten Versetzungsnetzwerken in den Grenzflächen hydophob gebondeter Wafer ist auch eine Methode zur Untersuchung weniger bzw. einzelner Versetzungen. Durch die Verwendung von Si-Wafern, die mit nahezu allen Kristallorientierungen herstellbar sind, kann eine Vielzahl unterschiedlicher Versetzungsnetzwerke reproduzierbar hergestellt werden. Weiterhin bietet die Variation der Dreh- und Kippwinkel zahlreiche Möglichkeiten der Variation der Versetzungsnetzwerke von reinen Dreh- bis zu reinen Kippwinkelkorngrenzen. Infolge der Änderung der Dreh- und Kippwinkel wird auch eine Kontrolle der Abstände der Versetzungen erreicht. Wird die Realisierung solcher Versetzungsnetzwerke mit Strukturierungstechniken kombiniert, so können Teststrukturen geschaffen werden, in denen nur einzelne Versetzungen vorhanden sind, und deren Kontaktierung es erlaubt, elektrische Messungen an diesen Defekten vorzunehmen. Die Notwendigkeit der Analyse einzelner Versetzungen soll die Abbildung 2 verdeutlichen, in der die hochauflösungselektronenmikroskopische Abbildung eines Teils der Grenzfläche von hydrophob gebondeten Wafern dargestellt ist. Detaillierte Untersuchungen zeigen, dass sich die Struktur einzelner, benachbarter Versetzungen in dieser Grenzfläche deutlich unterscheidet. Die in der Abbildung dargestellten Strukturen, die vermutlich die Versetzungskerne repräsentieren, besitzen unterschiedliche Ausdehnungen bis zu etwa 1 nm. Die auftretenden Kontraste deuten auf unterschiedliche Strukturen in den Versetzungskernen hin.

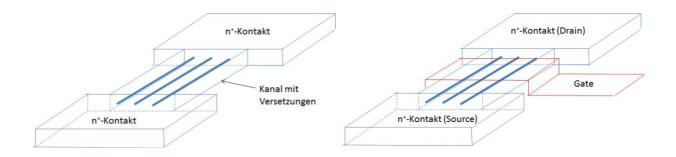

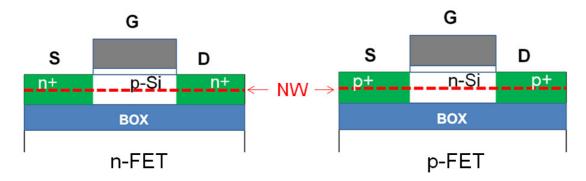

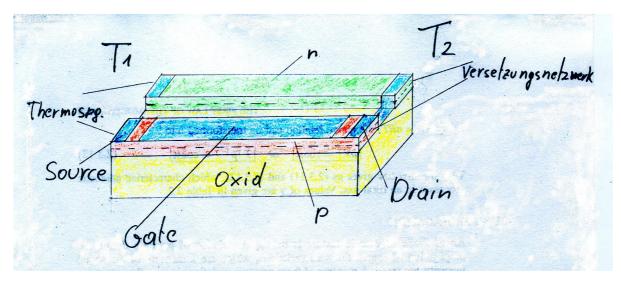

Um Aussagen über die elektrischen Eigenschaften möglichst von einzelnen Versetzungen zu gewinnen, wurden npn-Strukturen und Transistoren (MOSFET, metal-oxide-semiconductor field effect transistor) hergestellt. Der Aufbau beider Strukturen ist schematisch in

Abbildung 9 dargestellt. Zur Vermeidung des Einflusses etwaiger Defekte im Volumen des Si-Wafers auf

Abbildung 9 Schematische Darstellung der für die Messungen verwendeten npn-Strukturen (links) und Transistoren (rechts).

die elektrischen Eigenschaften der Versetzungen wurden die Versetzungsnetzwerke in dünnen Si-Schichten platziert, die elektrisch gegenüber dem Si-Wafer durch eine Oxidschicht isoliert sind. Das entspricht dem Aufbau eines SOI-Wafers. Zu deren Realisierung wurden kommerziell verfügbare SOI-Wafer als Ausgangsmaterial verwendet (nach dem Czochralski-Verfahren gezüchtete Si-Wafer mit einem Durchmesser von 150 mm, (100)-Orientierung, pleitend, spezifischer Widerstand  $\rho_s$  = 13,5 – 22,5  $\Omega$ cm). Die Dicken der Si-Schichten dieser SOI-Wafer waren 269 nm oder 600 nm, während die Dicken der vergrabenen Oxidschichten (BOX) entweder 60 nm oder 1000 nm betrugen. Durch sukzessive thermische Oxidation wurden die Dicken der Si-Schichten auf Werte von 15 nm oder 40 nm reduziert. Anschließend wurden die so bearbeiteten SOI-Wafer unter hydrophoben Bedingungen gebondet, wobei Drehwinkel zwischen  $0.01^{\circ} \le \vartheta_{twist} \le 0.4^{\circ}$  eingestellt wurden. Nach dem Bondprozeß wurden die Wafer Wärmebehandlungen bei 1050°C oder 1100°C unterzogen. Als letzter Schritt der Präparation wurde einer der Wafer eines gebondeten Paares mittels mechanischen Schleifens (mechanical grinding) und chemischen Ätzens (spin etching) abgetragen. Als Ätzstopschicht diente die BOX-Schicht des abgetragenen Wafers, die wiederum mittels chemischen Ätzens entfernt wurde.

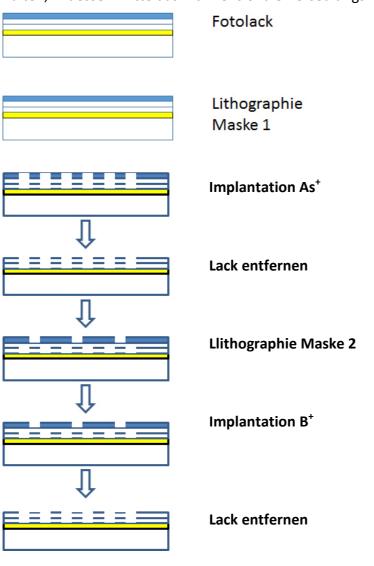

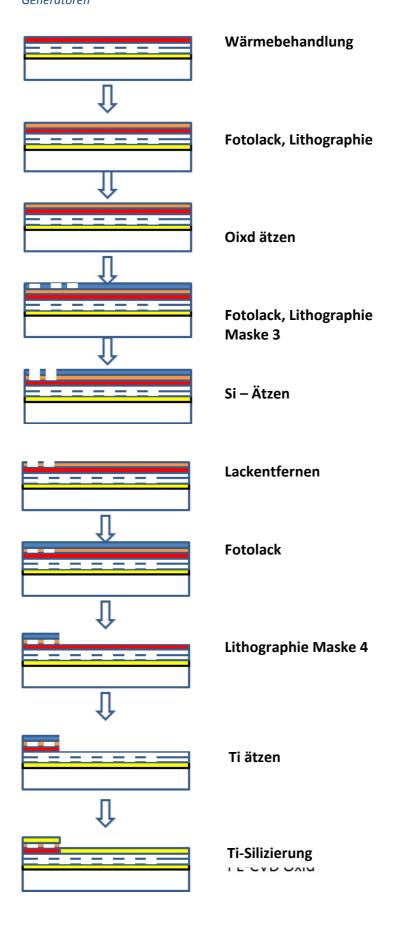

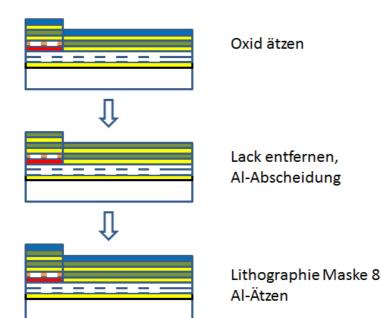

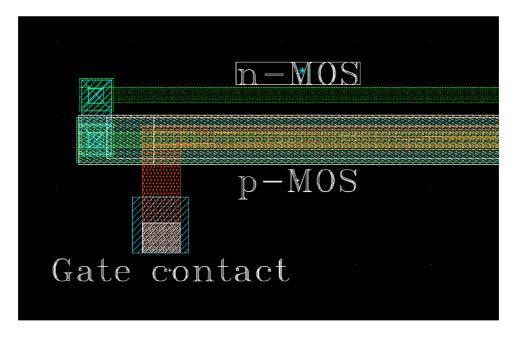

In die so hergestellten SOI-Wafer mit den Versetzungsnetzwerken in (einkristallinen) Si-Schichten mit Gesamtdicken von 30nm bis 80 nm wurden die npn-Strukturen und MOSFETs präpariert. Hierzu wurde ein CMOS-Prozeß mit 12 Maskenebenen entwickelt, der zum Beispiel in [32] detaillierter beschrieben wurde. Auf Grund des verfügbaren Materials (pleitend) wurden in ersten Prozeßdurchläufen nMOSFETs realisiert. Hierzu wurden die Kanalregionen durch photolithographische Prozesse und anschließenden Trockenätzprozeß (Cryo-Prozeß bei T = -60°C, SF<sub>6</sub>/O<sub>2</sub>-Chemie) definiert. Um die Anzahl der Versetzungen im Kanal zu variieren, wurden MOSFETs mit unterschiedlichen Breiten W und Längen L (1  $\mu$ m  $\leq$  W, L  $\leq$  10  $\mu$ m) hergestellt. Zur Berücksichtigung beider Scharen von Versetzungen in den  $\Sigma$ 1(100)-Korngrenzen wurden Transistoren in beiden orthogonalen <110>-Richtung in unmittelbarer Nähe zueinander angeordnet. Nach der Definition des Kanals wurden die Source- und Drain-Regionen mittels einer As<sup>+</sup>-Ionenimplantation (5 keV,  $1\cdot10^{15}$  cm<sup>-2</sup>) dotiert. Zur Eindiffusion der Dotanden erfolgte eine Wärmebehandlung (RTA, rapid thermal annealing) bei 950°C für

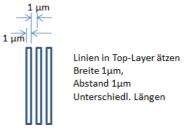

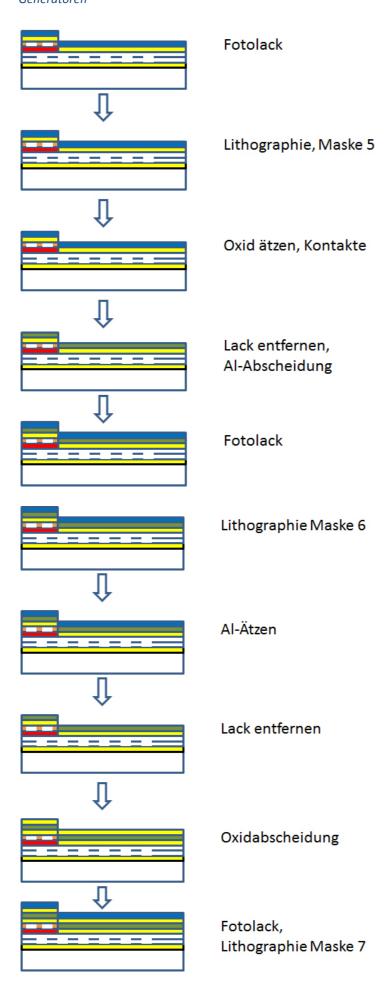

60 Sekunden. An diese Prozedur schloß sich der Aufbau des Gatekomplexes an. Hierzu wurde durch thermische Oxidation ein Gateoxid mit Dicken von 6 – 10 nm gebildet, auf das die Gateelektrode (polykristallines Si, Dicke 100 nm) mittels eines LP-CVD-Prozesses (*low-pressure chemical vapor deposition*) abgeschieden wurde. Vor der Strukturierung wurde das polykristalline Si durch eine As<sup>+</sup>-Implantation (30 keV, 1·10<sup>15</sup> cm<sup>-2</sup>) in Kombination mit einer Wärmebehandlung (RTA, 950°C, 60 Sekunden) dotiert. Die Source-, Drain- und Gate-Kontakte wurden letztlich mit einer Al-Abscheidung, gefolgt von einer Wärmebehandlung bei 420°C für 30 Minuten, realisiert. Parallel zu den nMOSFETs wurden unter Verwendung gleichen Wafermaterials auch pMOSFETs hergestellt. Der Prozeßablauf ist nahezu identisch zu dem der Herstellung von nMOSFETs, jedoch mit B<sup>+</sup>-Ionenimplantationen der Source- und Drain-Gebiete sowie des Gates. Für die Source- und Drain-Gebiete fanden B<sup>+</sup>-Ionenimplantationen mit Dosen von 1·10<sup>15</sup> cm<sup>-2</sup> und Energien von 10 keV Anwendung, während die Gate-Gebiete mit gleicher Dosis, jedoch mit einer Energie von 30 keV implantiert wurden. Die auf die Implantationen folgende Wärmebehandlung wurde für die pMOSFETs ebenfalls mittels RTA, jedoch bei 1000°C für 10 Sekunden durchgeführt.

Zur Beurteilung der elektrischen Eigenschaften der Versetzungen wurden als Referenz MOS-FETs auch auf SOI-Wafern mit gleichen Dicken der Si-Schicht, jedoch ohne Versetzungsnetzwerk, präpariert. Die Herstellung erfolgte im gleichen Prozeßdurchlauf, so dass etwaige Kontaminationen nicht berücksichtigt werden brauchen. Es sei an dieser Stelle angemerkt, dass Kontaminationskontrollen des gesamten CMOS-Prozesses, der am MPI Halle durchgeführt wurde, unter Anwendung der TXRF-Technik (*total reflection X-ray fluorescence spectrometry*) erfolgten. Die damit festgestellten Konzentrationen an metallischen und alkalischen Verunreinigungen ergaben Werte von weniger als 5·10<sup>10</sup> Atome/cm<sup>2</sup>.

Erste Strom-Spannungs-Messungen (IV-Charakteristik) wurden an npn-Strukturen durchgeführt, die im Vergleich zur Referenzprobe eine Erhöhung des Stromes um bis zu 6 Größenordnungen ergaben [32]. Der Anstieg des Stromes hängt von der Anzahl der Versetzungen und wahrscheinlich auch vom Versetzungstyp ab. Die Versetzungen bilden somit Nanometer große Kanäle mit einer höheren Leitfähigkeit, die zu höheren Ladungsträgerkonzentrationen führt. Dieses Ergebnis bestätigt die durch die EBIC-Messungen gewonnenen Resultate. Analoge Beobachtungen des Anstieges des Stromes werden auch von anderen Autoren an ähnlichen Strukturen beschrieben [15].

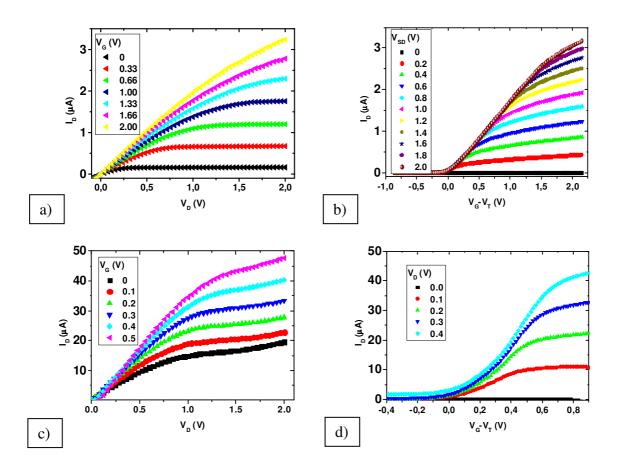

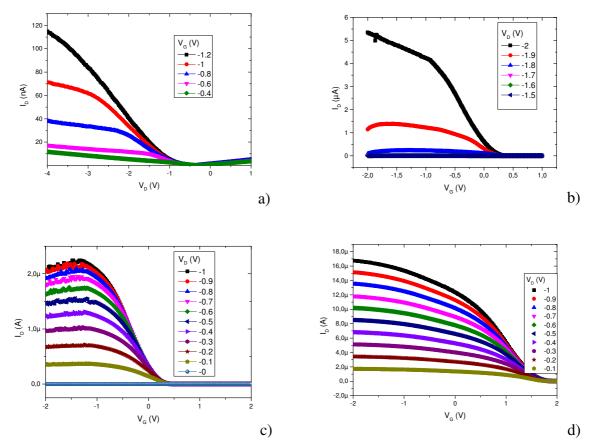

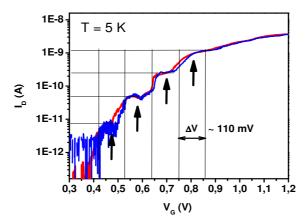

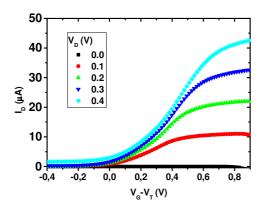

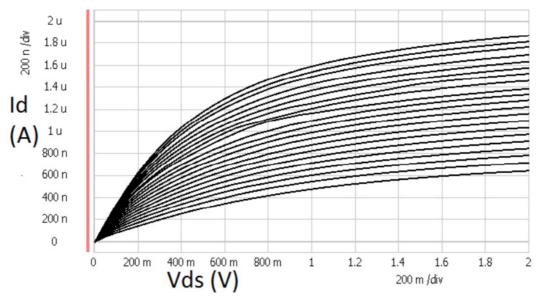

Elektrische Messungen erfolgten an zahlreichen nMOSFETs auf Substraten mit unterschiedlichen  $\vartheta_{twist}$  und  $\vartheta_{tilt}$ , wodurch sowohl unterschiedliche Anzahlen von Versetzungen in den Transistorkanälen als auch unterschiedliche Versetzungstypen berücksichtigt werden konnten. Zur Darstellung der Ergebnisse wird auf die für die Untersuchung von Transistoren üblichen Ausgangs- ( $I_d$ - $V_d$ ) und Transfer-Charakteristika ( $I_d$ - $V_g$ ) zurückgegriffen, worin  $I_D$  der Drainstrom,  $V_D$  die Drainspannung und  $V_G$  die Gatespannung sind. Häufig wird auch für Vergleiche anstatt der Gatespannung die Differenz  $V_G$ - $V_T$  abgetragen, wobei  $V_T$  die Schwellspannung (threshold voltage) ist. Ein Beispiel für die Charakterisierung der nMOSFETs zeigt die Abbildung 10, in der neben den  $I_d$ - $V_d$ - und  $I_d$ - $V_g$ -Kennlinien der Referenzprobe (SOI-Wafer ohne Versetzungsnetzwerk in der Si-Schicht) auch die entsprechenden Kennlinien für einen MOSFET mit Versetzungen im Kanal dargestellt sind. Infolge eines Drehwinkels  $\vartheta_{twist}$  = 0,35° entsteht ein Versetzungsnetzwerk aus Schraubenversetzungen, die untereinander einen Abstand von ca. 15 nm aufweisen. Bei einer Breite des Kanals von W = 1  $\mu$ m bedeutet das, dass etwa 60 Versetzungen im Kanal existieren. Aus den  $I_D$ - $V_G$ -Kennlinien des Referenz-Transistors

(Abbildung 10b) wird eine Schwellspannung von  $V_T = -150$  mV bestimmt, der Anstieg unterhalb der Schwellspannung (SS, subthreshold slope) beträgt SS = 100 mV/Dekade.

Abbildung 10 Ausgangs- und Transfer-Charakteristiken von n-MOSFETs ohne (a,b) und mit einem Versetzungsnetzwerk im Kanal (c,d). Die Dicke der Si-Schicht betrug in beiden Fällen 80 nm. Die Kanallängen und –breiten der gemessenen Transistoren waren jeweils 1 μm

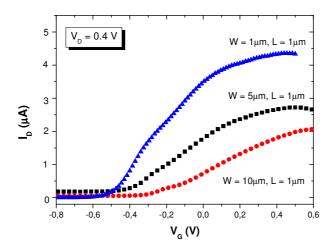

Gleiche Messungen an MOSFETs mit Versetzungen im Kanal führen zu höheren Drainströmen bei gleichen Werten von  $V_D$  und  $V_G$  (vergl. Abbildung 10). Gerade bei niedrigen Gatespannungen kann eine Erhöhung von  $I_D$  um eine Größenordnung erreicht werden. Für  $V_G$ - $V_T$  = 0,7 V und  $V_D$  = 0,4 V wird für den MOSFET mit Versetzungen zum Beispiel ein Drainstrom  $I_D$  = 6,5·10<sup>-6</sup> A gemessen, während unter den gleichen Bedingungen für die Referenzprobe  $I_D$  =  $6\cdot10^{-7}$ A ist (vergl. Abbildung 10a). Versetzungen im Kanal eines MOSFETs führen nicht nur zu einer Erhöhung des Drainstromes, sondern ändern auch die Schwellspannung  $V_T$  sowie SS gravierend. Die Abbildung 11 zeigt zum Beispiel die  $I_D$ - $V_G$ -Kennlinien für MOSFETs mit Versetzungsnetzwerken bei einer Drainspannung  $V_D$  = 0,4 V. Variiert wurde hier die Breite des Kanals W, die, bei gleichem Versetzungsnetzwerk, einer Erhöhung der Anzahl der Versetzungen im Kanal um den Faktor 10 entspricht. Aus der Abbildung ist ersichtlich, dass mit zunehmender Anzahl der Versetzungen die Schwellspannung von  $V_T$  = -400 mV (für W = 1  $\mu$ m) auf  $V_T$  = -150 mV für W = 10  $\mu$ m ansteigt. Anderseits steigt SS mit der Verringerung der Anzahl der Versetzungen an. Für W = 10  $\mu$ m wird SS = 120 mV/Dekade ermittelt, während für W = 1 ein Wert von S  $\cong$  370 mV/Dekade resultiert.

Abbildung 11 Abhängigkeit des Drainstromes von der Anzahl der Versetzungen im Kanal. Die Kanalbreite W bestimmt die Anzahl der Versetzungen. Messungen bei  $V_D = 0.4 \text{ V}$ .

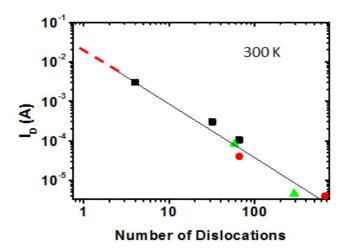

Die beschriebenen Messungen demonstrieren klar, dass die Anzahl der Versetzungen im Kanal die Parameter von nMOSFETs beeinflußt. Im bisher beschrieben Fall wurden MOSFETs betrachtet, die auf Grund von  $\vartheta_{twist}$  = 0,35° etwa 60 oder mehr Versetzungen im Kanal besitzen. Werden zusätzlich MOSFETs betrachtet, die auf Substraten mit  $\vartheta_{twist}$  = 0,035° präpariert wurden, so kann auf Grund des nun vorliegenden Versetzungsabstandes von 150 nm der Einfluß von nur noch 6 Versetzungen bei W = 1  $\mu$ m gemessen werden. In Abbildung 12 sind die Ergebnisse von Messungen des Drainstromes an MOSFETs mit unterschiedlichen Anzahlen von Versetzungen dargestellt. Für  $V_D$  = 2V wird ein Drain-Strom von  $I_D$  = 3·10<sup>-3</sup> A

Abbildung 12 Drainstrom ( $I_D$ ) als Funktion der Anzahl der Versetzungen im Kanal von nMOSFETs. Unterschiedliche Symbole charakterisieren Messungen an MOSFETs auf unterschiedlichen Wafern. Messungen für  $V_D = 2 \text{ V}$  und  $V_G = 0 \text{ V}$ .

bestimmt, während für 60 Versetzungen im Kanal  $I_D = 1\cdot 10^{-4}$  A ist. Wird, wie in Abbildung 12 gezeigt, der Drainstrom als Funktion der Anzahl der Versetzungen im Kanal in einer doppeltlogarithmischen Darstellung aufgetragen, so resultiert ein linearer Anstieg des Drainstromes mit der Verringerung der Versetzungsanzahl. Aus den vorliegenden Daten kann auf den Strom einer einzelnen Versetzung durch Extrapolation geschlossen werden, was zu einem Wert von  $I_D \cong 5\cdot 10^{-2}$  A führen würde.

Interpretationen des Einflusses von Versetzungen auf den Drainstrom der MOSFETs sind nur bedingt auf der Basis der üblichen "Transistor-Physik" möglich. Die untersuchten MOSFETs mit Dimensionen im Mikrometerbereich sind danach sog. Langkanal-MOSFETs (long channel MOSFET), für die die Abhängigkeit des Drainstromes von den Drain- und Gatespannungen durch Gl. (5) gegeben ist:

$$I_{D} = \frac{W}{L} \mu_{eff} C_{ox} \left( V_{G} - V_{T} \right) V_{D} = \frac{V_{D}}{R_{ch}}$$

$$(5)$$

Hierin ist R<sub>ch</sub> der Kanalwiderstand:

$$R_{ch} = \frac{1}{\mu_{eff} C_{ox} \left( V_{G} - V_{T} \right)} \cdot \frac{L}{W}$$

(6)

Nach Gl. (5) ist die Erhöhung des Drainstromes ID für nMOSFETs mit Versetzungen im Kanal somit auf eine Verringerung des Kanalwiderstandes zurückzuführen. Angemerkt sei hier, dass die Erhöhungen des Stromes im Fall der npn-Strukturen ebenfalls mit einer Verringerung des Widerstandes (bzw. der Erhöhung der Leitfähigkeit) begründet wurde (siehe oben)). Da für die dargestellten Messungen die gleichen Geometrien für nMOSFETs mit und ohne Versetzungen vorhanden sind (W = const., L = const.), sind für  $V_G$  = const. Änderungen von R<sub>ch</sub> nur durch Änderungen der effektiven Beweglichkeit der Ladungsträger (μ<sub>eff</sub>, für nMOSFETs Elektronen), der Schwellspannung (V<sub>T</sub>), oder der Kapazität des Gateoxides (C<sub>ox</sub>) zu erreichen. Messungen von Cox ergeben mit unterschiedlichen Methoden (statische CV-Messungen, split CV-Messungen) nahezu gleiche Werte von C<sub>ox</sub> ≅ 1pF für MOSFETs mit und ohne Versetzungen. Somit sollten die Erhöhungen von ID für MOSFETs mit Versetzungen entweder auf die bereits durch die im Experiment verifizierten Änderungen von  $V_T$  oder aber auf eine Erhöhung der Ladungsträgerbeweglichkeit zurückzuführen sein.. Bestimmungen der Ladungsträgerbeweglichkeit (µeff) erfolgten mittels Hall-Effekt-Messungen bei Raumtemperatur und T = 80K an großflächigen Proben (2cm x 2cm). Für das Referenzmaterial (SOI-Wafer ohne Versetzungen) wurde  $\mu_{eff} \cong 350 \text{ cm}^2/\text{Vs}$  gemessen, was mit Literaturangaben übereinstimmt [33]. Hall-Messungen an Wafern mit Versetzungen in den Si-Schichten ergeben sehr stark streuende Werte, die etwa gleich oder niedriger zu denen des Referenzmaterials sind. Zum gleichen Ergebnis führen Berechnungen der Beweglichkeit aus dem linearen Bereich der Transfer-Charakteristik von nMOSFETs. Die großen Streuungen von μeff, die für Messungen an unterschiedlichen Wafern mit unterschiedlichem  $\vartheta_{\mathsf{twist}}$  und  $\vartheta_{\mathsf{tilt}}$  bestimmt wurden, weisen auch darauf hin, dass die Dichte der Versetzungen und der Versetzungstyp Einfluß auf die Ladungsträgerbeweglichkeit besitzen.

Die Schwellspannung V<sub>T</sub> eines MOSFETs ist nach Sze und Ng [34]

$$V_{T} = V_{FB} + 2\Psi_{B} + \frac{\sqrt{2\varepsilon_{s}qN_{A}(2\Psi_{B})}}{C_{ox}}$$

$$= \left(\phi_{ms} - \frac{Q_{f}}{C_{ox}}\right) + 2\Psi_{B} + \frac{\sqrt{4\varepsilon_{s}qN_{A}\Psi_{B}}}{C_{ox}}$$

(7)

worin  $V_{FB}$  die Flachbandspannung (flat-band voltage),  $\varepsilon_s$  die Dielektrizitätskonstante des Si, q = e die Elementarladung,  $\phi_{ms}$  die Differenz der Austrittssarbeiten (work function difference) zwischen Metall und Halbleiter und  $Q_f$  die Dichte fester Oxidladungen sind. Weiterhin bezeichnen  $\Psi_B = |E_F - E_i| q$  die Differenz des Fermi-Niveaus zu dem des intrinsischen Materials

und  $N_A$  die Akzeptor-Konzentration. Für die unter gleichen Bedingungen hergestellten MOS-FETs mit und ohne Versetzungen können bis auf  $N_A$  und  $\Psi_B$  alle anderen Parameter als konstant angesehen werden, so dass die durch die Versetzungen hervorgerufenen Änderungen der Schwellspannungen  $V_T$  der MOSFETs auf diese beiden Parameter zurückzuführen sind.

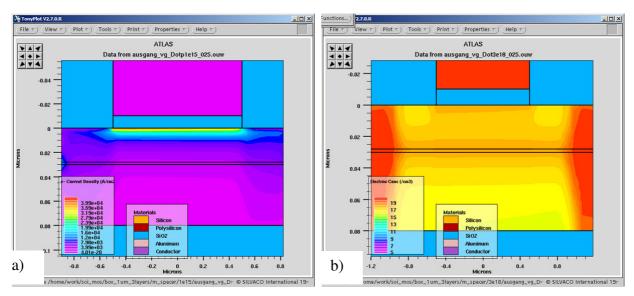

Zur weiteren Analyse der Ursachen der höheren Ströme in MOSFETs mit Versetzungsnetzwerken wurden Computersimulationen der Bauelementeparameter mit Hilfe eines kommerziellen Programmpaketes (Silvaco ATHENA/ATLAS) vorgenommen. Zur Simulation der Versetzungen wurde eine 2 nm dicke Schicht in den Kanal eingefügt, deren Parameter (Dotandenkonzentration, Beweglichkeit sowie Kombinationen beider) variiert wurden. Aus der Simulation und dem Vergleich der berechneten mit den experimentellen Kennlinien ist deutlich erkennbar, dass für den MOSFET mit dem Versetzungsnetzwerk ein um den Faktor 10 höherer Drainstrom resultiert, was qualitativ mit den experimentellen Messungen übereinstimmt. Die berechneten 2-dimensionalen Elektronendichteverteilungen im Kanalbereich der MOSFETs mit und ohne Versetzungsnetzwerk demonstriert die Abbildung 13 für  $V_D = V_G = 0,25$  V. Deutlich sichtbar ist in der Abbildung, dass bereits bei niederen Drain- und Gatespannungen ein leitfähiger Kanal entlang der Versetzungen entsteht. Analoge Simulationen

Abbildung 13 Berechnete 2-dimensionale Elektronendichteverteilungen im Kanalbereich eines Transistors ohne Versetzungsnetzwerk (a) und mit einem Versetzungsnetzwerk (b), worin die höhere Elektronenkonzentration in der Versetzungsschicht (simuliert durch eine 2 nm dicke n-leitenden Schicht mit der Dotandenkonzentration von  $3\cdot10^{18}$  cm<sup>-3</sup>) deutlich erkennbar ist. Für die Simulationen wurden  $V_G = V_D = 0,25$  V angenommen.

unter Variation entweder nur der Beweglichkeit oder der Dotandenkonzentration führen zu keinem vergleichbaren Ergebnis. Die Kombination von Beweglichkeit mit der Dotandenkonzentration ist ein allgemeines Transportphänomen in Halbleitern. Das Versetzungsnetzwerk im Kanal der nMOSFETs wirkt deshalb wie eine n-leitende Schicht, womit davon ausgegangen werden kann, dass an den Versetzungen in diesem Material hohe Konzentrationen von Elektronen lokalisiert sind. Die Erhöhung der Dotandenkonzentration erklärt damit auch, dass die Ladungsträgerbeweglichkeiten, wie experimentell verifiziert, nicht wesentlich ansteigen, sondern eher geringer sind. Ebenso kann auf dieser Grundlage die Verschiebung der Schwellspannungen erklärt werden. Wird unter Berücksichtigung des gleichen Modells die Ladungsträgerkonzentration in der 2 nm dicken Schicht weiter erhöht, so wird  $V_T$  auch weiter zu negativen Spannungen verschoben. Daraus folgt, dass  $\Psi_B$  in Gl. (7) den wesentlichen Beitrag zur Verschiebung der Schwellspannung liefert.

Auf der Grundlage des entwickelten Modells lassen sich auch die unterschiedlichen Drainströme erklären, die für unterschiedliche Typen von Versetzungen im Kanal der MOSFETs gemessen wurden.

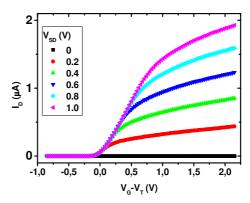

Analog zu den bisher beschriebenen Untersuchungen an nMOSFETs wurden gleiche Analysen an pMOSFETs, präpariert auf p-leitendem Si, durchgeführt. Details dieser Untersuchungen sind in [35] beschrieben und sollen an dieser Stelle deshalb nur kurz zusammengefaßt werden. Für Referenzproben ohne Versetzungsnetzwerk resultieren etwa um eine Größenordnung geringere Drainströme als für vergleichbare nMOSFETs. Dieses Phänomen ist allgemein bekannt und wird durch die niedrigere Beweglichkeit von Löchern

Abbildung 14 I<sub>D</sub>-V<sub>G</sub> Kennlinien von pMOSFETs präpariert in p-leitendem Material (a,b) und n-leitendem Material (c, d). Dargestellt sind die Kennlinien der jeweiligen Referenzproben ohne Versetzungen (a, c) und von MOSFETs mit Versetzungen im Kanal (b, d). Auf die unterschiedliche Skalierung sei hingewiesen.

gegenüber Elektronen im Si verursacht. Werden Schraubenversetzungen in den Kanal von pMOSFETs eingebracht, so werden nur noch Drainströme von  $-2\cdot 10^{-10}$ A  $\leq I_D \leq -6\cdot 10^{-10}$  A für  $V_D = V_G = -4V$  gemessen, die um 4 Größenordnungen niedriger sind als für nMOSFETs mit ähnlichen Schraubenversetzungen (Abbildung 14a,b). Bemerkenswert ist, wie das angeführte Beispiel zeigt, dass wesentlich höhere Drain- und Gatespannungen erforderlich sind, um Ströme fließen zu lassen. Werden anstatt reiner Schraubenversetzungen Netzwerke aus Schrauben- und Stufenversetzungen ( $\vartheta_{twist} \cong \vartheta_{tilt} \cong 1,3^{\circ}$ ) in den Kanal eingebracht, so steigt der Drainstrom um eine bis zwei Größenordnungen an. Die Verringerung des Drainstromes im Fall des p-leitenden Materials kann nur bedeuten, dass durch die Injektion von Löchern im Betrieb des FETs diese durch die Elektronen an den Versetzungen kompensiert werden, also ein geringerer Strom fließt. Werden demgegenüber pMOSFETs auf n-leitendem Material aufgebaut, so wird ebenso wie im Fall des nMOSFETs eine Erhöhung des Drainstromes regis-

triert (vergl. Abbildung 14c, d). Der Drainstrom ist für den pMOSFET mit Versetzungen in diesem Fall etwa um einen Faktor 8 – 10 höher als für die Referenz ohne Versetzungen.

Aus den beschriebenen Untersuchungen lassen sich zu den elektrischen Eigenschaften von Versetzungen die folgenden Schlußfolgerungen ableiten: Im untersuchten p-leitendem Material erfolgt entlang der Versetzungen ein Transport von Elektronen. Die gemessenen niedrigeren Drainströme in den pMOSFETs weisen auch darauf hin, dass Löcher an diesen Versetzungen keine wesentliche Bedeutung besitzen. Wird ein Löcherström injiziert, so rekombinieren diese Löcher mit den an den Versetzungen lokalisierten Elektronen. Als Konsequenz wird ein geringerer Strom für pMOSFETs gemessen. Im Fall der nMOSFETs führen die an den Versetzungen lokalisierten Elektronen zur Bildung eines leitfähigen Kanales, der zu höheren Drainströmen führt. Die Ursache der höheren Ströme ist auf Grund der bisher vorliegenden Ergebnisse vermutlich nicht eine höhere Ladungsträgerbeweglichkeit, sondern vorwiegend die höhere Ladungsträgerkonzentration. Werden für eine semi-quantitative Bestimmung der Elektronenkonzentrationen an den Versetzungen die in den Computersimulationen angenommenen Elektronenkonzentrationen (Dotandenkonzentrationen) verwendet, so ergibt sich folgendes Bild: Für eine Elektronenkonzentration an den Versetzungen (in der Simulation in der 2 nm dicken n-leitenden Schicht) von 3·10<sup>18</sup> cm<sup>-3</sup> wird eine Erhöhung des Drainstromes um eine Größenordnung, wie experimentell gemessen, erreicht. Unter Zugrundelegung dieser Konzentration und W = L = 1 µm folgt daraus, dass sich etwa 6000 Elektronen in dieser (Versetzungs-) Schicht befinden. Wird desweiteren davon ausgegangen, dass im Kanal dieses Transistors etwa 30 Versetzungen sind, so bedeutet das, dass ca. 200 Elektronen pro Mikrometer Versetzungslänge vorhanden sind, oder sich etwa aller 5 nm ein freies Elektron an den Versetzungen befindet. Diese Überlegung wird durch weiterführende Tieftemperatur-Untersuchungen gestützt, durch die Coulomb-Blockaden infolge der Versetzungen nachgewiesen wurden (siehe AP 1.5). Messungen ergeben hierbei Abstände der Coulomb-Inseln zwischen ca. 4 nm und 8 nm, was mit dem abgeschätzten Abstand freier Elektronen von 5 nm gut übereinstimmt [35].

Eine Erhöhung des Drainstromes, wie für nMOSFETs im p-Material wird auch für pMOSFETs gemessen, die in n-Material erzeugt wurden. In diesem Fall werden Löcher entlang der Versetzungen transportiert. Dieser Befund ist ein erster experimenteller Nachweis für das ambipolare Verhalten von Versetzungen, worauf bereits in älteren Arbeiten hingewiesen wurde [36, 37].

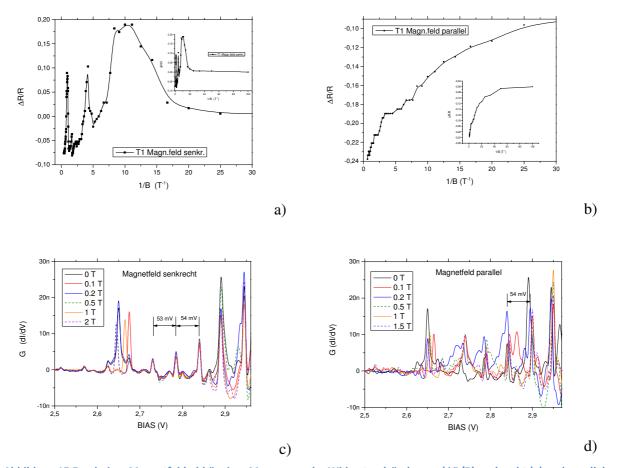

An nMOSFETs, die das in Abbildung 3 dargestellte Versetzungsnetzwerk beinhalten, wurden Magnetfeld-Messungen bei tiefen Temperaturen (T = 3,1 K) durchgeführt. Das Versetzungsnetzwerk ist im Wesentlichen aus Schraubenversetzungen aufgebaut, die einen Abstand von ca. 14 nm aufweisen. Bei W = 1  $\mu$ m bedeutet das, dass ca. 70 Versetzungen im Transistorkanal enthalten sind. Die Messungen bei VG =  $\nu$  zeigen 2 Effekte: (i.) Wird der differentielle Widerstand als Funktion des inversen Magnetfeldes aufgetragen, so können bei einem senkrecht angelegtem Magnetfeld Shubnikov – de Haas (SdH) - Osizllationen nachgewiesen werden (Abbildung 15). Wird das Magnetfeld parallel zu den Versetzungen angelegt, so sind die SdH-Oszillationen nicht mehr nachweisbar. Das Auftreten der SdH-Oszillationen korrespondiert zur Präsenz eines 2-dimensionalen Elektronengases (2-DEG). Die Nichtperiodizität deutet dabei auf Inhomogenitäten hin. Diese sind damit zu begründen, dass das Versetzungsnetzwerk zwar eine 2-dimensionale Struktur besitzt, der Ladungstransport jedoch über die Versetzungen (1-dimensional) erfolgt.

Abbildung 15 Ergebnisse Magnetfeld-abhängiger Messungen der Widerstandsänderung ( $\Delta R/R$ ) senkrecht (a) und parallel zum Versetzungsnetzwerk (b). Messungen der Leitfähigkeit G zeigen die Existenz von Coulomb-Blockaden bei unterschiedlichen Stärken des Magnetfeldes. Die gemessene Transistorstruktur wurde in einem Wafer erzeugt, der das in Abbildung 3 dargestellte Versetzungsnetzwerk aus Schraubenversetzungen beinhaltet. Messungen bei T = 3.1 K.

Neben den SdH-Oszillationen sind in der G (dI/dV)- $V_{SD}$  – Charakteristik deutlich die Coulomb-Blockaden sichtbar, die hier als Funktion des Magnetfeldes dargestellt sind (Abbildung 15c, d). Für den Transistor 1 sind bei einem senkrechten Magnetfeld keine Änderungen der Position der Blockaden für  $0 \le B \le 2$  T sichtbar. Das ist in Übereinstimmung mit Literaturangaben. Jedoch ändern sich die Amplituden. Änderungen in der Position werden nur für die Blockade bei 2,65 V in Abhängigkeit von B sichtbar. Der Abstand zwischen den anderen Blockaden ist  $V = const. \cong 54$  mV (die Messungen wurden mit einer Auflösung von 5 mV durchgeführt).

Wird für den Transistor 1 das Magnetfeld parallel zu den gemessenen Versetzungen angelegt, so können die Blockaden ebenfalls und mit gleichem Abstand nachgewiesen werden. Interessant sind jedoch hier die Aufspaltungen der Peaks (doublet), was auf spinabhängige Effekte hindeutet [38].

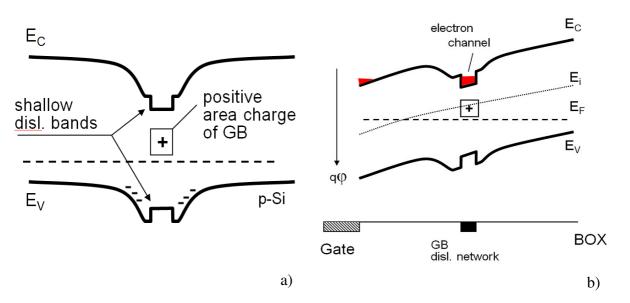

Faßt man die Ergebnisse aller Untersuchungen zusammen, so kann basierend auf der Bandstruktur ein weiterentwickeltes Modell für Versetzungen in Si entworfen werden [39]: Es wird allgemein angenommen, dass Versetzungen flache, 1-dimensionale Bänder erzeugen, die ca. 50 – 100 meV unterhalb des Leitungsbandes bzw. oberhalb des Valenzbandes liegen [40]. Dementsprechend sollte ein Versetzungsnetzwerk zur Bildung 2-dimensionaler Bänder führen. Der Nachweis der Existenz eines 2-DEG führt dann zu einer Bandstruktur in der Nähe der Versetzungen, wie sie schematisch in Abbildung 16 ohne angelegt Spannung (off-state) und mit angelegter Spannung (on-state) gezeigt ist.

Abbildung 16 Schema der Bandstruktur eines MOSFETs mit Versetzungen im Transistor-Kanal im off-state (a) und onstate (b).

Beim Anlegen einer positiven Spannung wird ein Elektronenkanal in dem flachen Band unterhalb des Leitungsbandes gebildet (Abbildung 16b). Es wird mit Elektronen gefüllt, die von der Source-Elektrode injiziert werden. Der Elektronentransport in den Versetzungen ist effizienter als im Inversionskanal unterhalb der Gateelektrode. Das für einen n-MOSFET dargestellte Bandschema kann in ähnlicher Weise auch auf p-MOSFETs übertragen werden, wobei ein Kanal von Löchern in dem flachen Band oberhalb des Valenzbandes gebildet wird.

#### AP 1.2 Umdotierung

Ausgehend von den zur Verfügung stehenden Materialien ist es einfacher, p-leitende SOI-Schichten als Ausgansmaterial zu verwenden. Für die Thermopaare der TEG müssen jedoch alternierend p- und n-leitende Elemente realisiert werden. Deshalb muß eine Umdotierung von p- zu n-Typ vorgenommen werden. Dazu ist eine Überkompensation des ursprünglich p-leitenden Materials mit Donatoratomen (z.B. As) notwendig. Hierfür sollten die p-SOI-Schichten mit Netzwerk flach implantiert und mit einer anschliessenden Wärmebehandlung die Dotanden aktiviert und dabei möglichst homogen in der SOI-Schicht verteilt werden. Dazu waren umfangreiche Untersuchungen erforderlich (Experimente, Messungen, Simulationen), um die optimalen Implantationsenergien und -dosen sowie die geeigneten Wärmebehandlungen für die entsprechenden Schichtdicken zu finden.

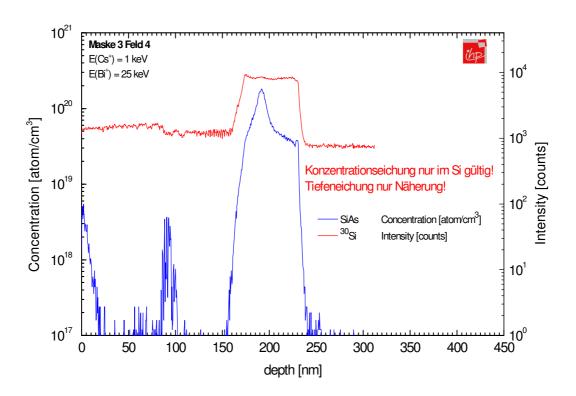

Ein Beispiel für die erfolgreiche Umdotierung zeigt die

Abbildung 17. Eine SOI Schicht aus p- Silizium ( $\rho \cong 10~\Omega$ cm, d.h. Dotandenkonzentration ca. 1,3·10<sup>15</sup> cm<sup>-3</sup>) mit einer Dicke von 40nm wurden durch Ionenimplantation von Arsen (Energie 10 keV, Dosis 1·10<sup>15</sup> cm<sup>-2</sup>) mit anschließender Ausheilung in eine n – leitende Schicht umdotiert. Mittels SIMS Untersuchungen konnte der Nachweis der Umdotierung erbracht werden. Wie die Abbildung zeigt, existiert eine As-Konzentration von mehr als 5·10<sup>19</sup> cm<sup>-3</sup> in der Schicht.

Abbildung 17 SIMS-Profil zum Nachweis der Umdotierung. Eine 40 nm dicke Si-Schicht (urpsrünglich p-leitendend) wurde durch eine As+-ionenimplantation (10 keV, Dosis 1·10<sup>15</sup> cm<sup>-2</sup>) umdotiert.

# AP 1.3 Design der Funktionselemente

Basierend auf den Ergebnissen von AP1.1 und AP1.2 wurden Funktionselemente bzw. Thermopaare entwickelt. Die Funktionselemente sollten in ihrer Struktur bzw. Geometrie so optimiert werden, dass die thermoelektrische Güte ZT ein Maximum erreicht. Darüber sollten die Funktionselemente im vorliegenden Prozess hochintegrierbar (> 1000 FE pro mm²) sein, um praktikable Spannungen zu erreichen. Um die relevanten Parameter zu extrahieren, waren auch geeignete Test-Strukturen zu entwickeln.

Für den Entwurf von integrierbaren Funktionselementen (FE) wurden zuerst makroskopische Thermogeneratoren (TG) entwickelt. Der Aufbau orientierte sich an der in Abbildung 18 gezeigten Struktur.

Abbildung 18 Vereinfachte Struktur eines Thermogenerators.

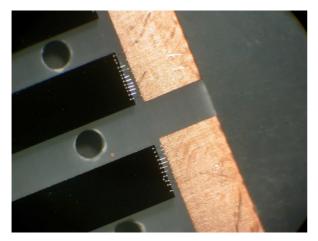

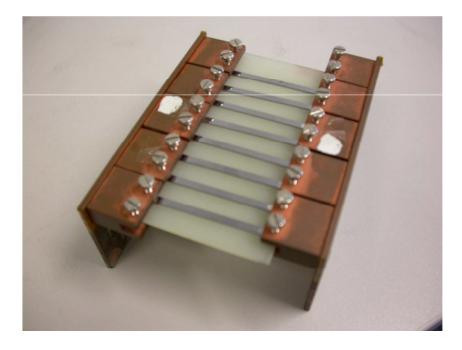

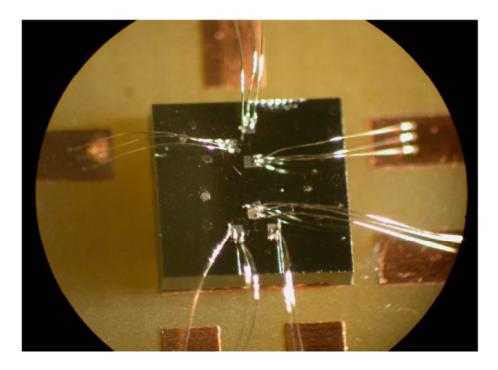

#### AP 1.4 Herstellung einfacher Teststrukturen

Ein erster Versuchsaufbau bestand aus 10 Siliziumstreifen, wobei immer ein n-dotierter Streifen mit einem p-dotierten Streifen über ein Metall verbunden ist. Das durch das IHP zur Verfügung gestellte Silizium wies einen spezifischen Widerstand von  $\rho\approx7~\Omega$ cm für n-dotiertes Silizium beziehungsweise  $\rho\approx50~\Omega$ cm für p-dotiertes Silizum auf. Die Streifen des makroskopischen Thermogenerators hatten eine Länge von 5 cm und eine Breite von 0.5 cm. Die Abbildung 19 zeigt die Kontaktierung der Streifen und des Metalls mittels Wedge-Bonding. Alle Streifen wurden auf ein Substrat geklebt, welches eine geringe Wärmeleitfähigkeit aufweist. Die Generierung eines Temperaturgradienten über den Siliziumstreifen erfolgte durch einseitige Kühlung mittels Peltier-Elementen, dargestellt in Abbildung 20.

Abbildung 20 Erster Versuchsaufbau.

Dieser Aufbau ermöglichte einer Temperaturdifferenz von 45 °C. Diese erwies sich im weiteren Verlauf als zu klein. Jedoch konnte durch eine gemessene Strom-Spannungskennlinie die Funktionsfähigkeit des Thermogenerators festgestellt werden. Der Übergang n-Silizium – Metall – p-Silizium ist jedoch kein rein ohmscher Kontakt. Anhand des Knicks im Kennlinienverlauf in Abbildung 21 ist ersichtlich, dass der Kontakt ebenfalls Schottky-Charakteristik auf-

weist.

Abbildung 21 Strom-Spannungs-Kennlinie des in Abbildung 20 gezeigten makroskopischen Thermogenerators.

Zur Verifikation der Messung wurde die Gleichung (8) verwendet [41]. Die Energieniveaus des Leitungs- und Valenzbandes sind mit  $E_c$  und  $E_v$  angegeben. Des Weiteren wird die Ladungsungsträgerdichte und –beweglichkeit durch die Koeffizienten  $A_n$  und  $A_p$  ausgedrückt.

$$U = \left(\alpha_{p} - \alpha_{n}\right) \Delta T = \left(\frac{k}{q} \left(A_{p} - \frac{E_{v} - E_{F}}{kT}\right) + \frac{k}{q} \left(A_{n} - \frac{E_{F} - E_{c}}{kT}\right)\right) \Delta T \tag{8}$$

Die Verwendung eines Epoxyds mit hoher thermischer Leitfähigkeit zur Verbindung des in Abbildung 20 gezeigten Thermogenerators mit der Kühlfläche erwies sich ebenfalls als untauglich. Nach einer gewissen Zeit brachen die Bonddrähte zwischen Silizium und Metall durch die thermische Ausdehnung des Epoxyds ab.

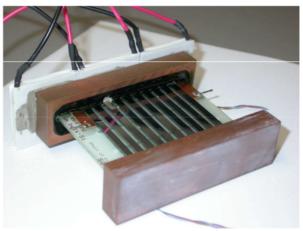

Ein zweiter modularer Aufbau (Abbildung 22) erfolgte ohne Drahtbonding. Die Siliziumstreifen wurden an massiven Kupferblöcken befestigt. Diese waren elektrisch voneinander isoliert. Beide Seiten des Thermogenerators konnten nun über die angebrachten Kupferplatten gekühlt und erwärmt werden.

Abbildung 22 Zweiter modularer Versuchsaufbau.

Die Projektpartner stellte für diesen Versuchsaufbau unterschiedlich dotierte p-Siliziumstreifen zur Verfügung. Die Dotierung des n-Siliziums ( $\rho$ =8  $\Omega$ cm -12  $\Omega$ cm) wurde nicht geändert.

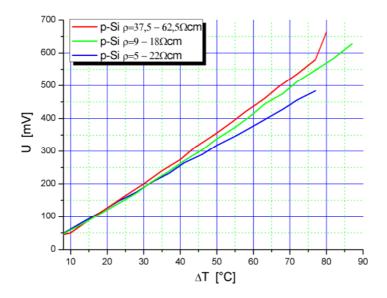

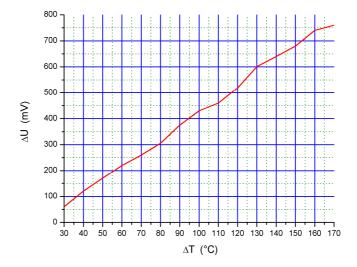

Erste Messungen der Leerlaufspannung in Abhängigkeit von der Temperatur und Dotierung des p-Siliziums sind in Abbildung 23 dargestellt. Es wurden für diese Messungen 4 n-p-Siliziumpaare verwendet.

Abbildung 23 Thermospannung in Abhängigkeit von der Temperaturdifferenz. Verwendet wurde der in Abbildung 22 gezeigte modulare Versuchsaufbau.

Aus dem Diagramm ist ersichtlich, dass mit steigendem Widerstand des Thermogenerators der Spannungsabfall steigt. Bei einer Temperaturdifferenz von 77 K und einer niedrigen p-Dotierung ( $\rho$ =37,5-62,5  $\Omega$ cm) konnte eine Spannung von 580 mV gemessen werden. Zusätzlich wurde der Kurzschlussstrom bei der gleichen Temperaturdifferenz gemessen. Bei einer

hohen p-Dotierung ( $p=9-18~\Omega cm$ ) betrug der Strom 11,7  $\mu A$ . Dieser Strom ist jedoch nicht ausreichend um eine Schaltung zur Spannungsregulierung zu realisieren.

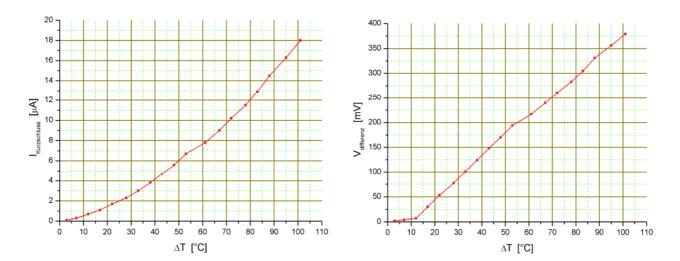

Da jedoch der Kurzschlussstrom indirekt proportional zum spezifischen Widerstand der Siliziumstreifen ist, wurden in einem weiteren Versuch noch höher dotierte p-Siliziumstreifen verwendet. Deren spezifischer Widerstand lag im Bereich von  $0,005~\Omega cm-0,02~\Omega cm$ . Die Abbildung 24 zeigt den Kurzschlussstrom und die Spannungsdifferenz in Abhängigkeit der Temperatur.

Das Diagramm des Kurzschlussstromes in Abbildung 24 zeigt auch, dass der maximale Strom nicht wesentlich erhöht werden konnte. Folglich ist davon auszugehen, dass, zusätzlich zum Widerstand der Siliziumstreifen, Kontaktwiderstände die elektrischen Eigenschaften des TG bestimmen.

Abbildung 24 Kurzschlußstrom und Spannungsdifferenz von 4 n-p-Siliziumpaaren.

#### AP 1.5 Charakterisierung Material und Teststrukturen

Zur Charakterisierung der Eigenschaften der SOI-Schichten mit Netzwerk wurden bereits etablierte Methoden (z.B. TEM zur Strukturcharakterisierung, EBIC und Kennlinien-Messung zur elektrischen Charakterisierung) eingesetzt. Um jedoch zuverlässige Aussagen nicht nur über die elektrischen Eigenschaften und den Transport zu gewinnen, sondern auch über die Wärmeleitung und den Seebeck-Koeffizienten, war die Modifikation vorhandener Messverfahren (z.B. Thermographie) und der Aufbau neuer Messplätze z.B. zur Messung der Wärmeleitung an relativ kleinen Strukturen notwendig.

Dabei wurde insgesamt eng und arbeitsteilig mit den Verbundpartnern zusammen gearbeitet werden.

#### Methodenentwicklung

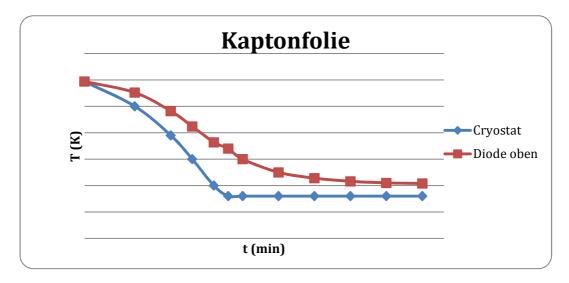

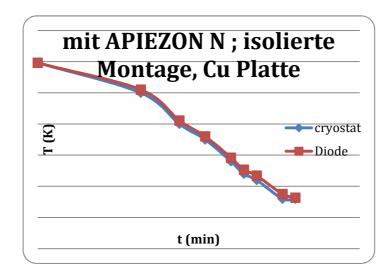

Aus EBIC Untersuchungen im Temperaturbereich von 10 - 300K wurden detaillierte Informationen über elektrische Eigenschaften von Versetzungsnetzwerken erwartet. Aus diesem Grunde musste der vorhandene Kryostat eines im JointLab IHP/BTU installierten Rasterelektronenmikroskopes (REM) derart modifiziert werden, dass die Probenhalterung elektrisch vom eigentlichen Kryostaten isoliert wurde – aber trotzdem die gleiche Temperatur wie der

Kryostat aufwies. Der Nachweis konnte durch eine zusätzlich auf dem Probenträger angebrachte Messdiode erbracht werden.

Abbildung 25 Temperaturverlauf des im Rasterelektronenmikroskops verwendeten Kryostat vor (oben) und nach der Modifikation (unten).

Die elektrischem Messungen an Teststrukturen im Temperaturbereich von 5...295K mussten bei sehr geringen Spannungen (im Bereich <=1mV ...4V) bei Strömen bis in den Pikoamperebereich durchgeführt werden (Paramerteranalyser Agilent 4156). Daher erwies es sich als notwendig, den verwandten Meßkryostaten (Janis Research) mit neuen Proberarmen mit TRIAX Anschlüssen umzurüsten (Abbildung 26).

Abbildung 26 Meßkryostat "Janis Research St500 Micromanipulated Probe Station".

#### Charakterisierung Material- und Teststrukturen

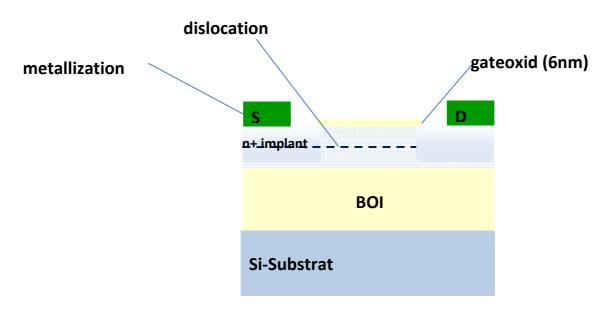

Zur Charakterisierung wurden vom MPI Halle Teststrukturen mit folgendem Aufbau hergestellt und durch alle Projektpartner analysiert: Auf einem Si Substrat mit 50nm Buffer Oxide (BOI) befand sich eine 40nm dicke Si Schicht (p Si), in deren Mitte spezielle Versetzungssnetzwerke (abhängig von den Präparationsbedingungen) implementiert wurden (Abbildung 27); mit Ausnahme des Referenzwafers – hier wurde der gleiche Aufbau aber ohne Versetzungsnetzwerk realisiert.

Abbildung 27 Schematischer Aufbau der Teststrukturen (SOI).

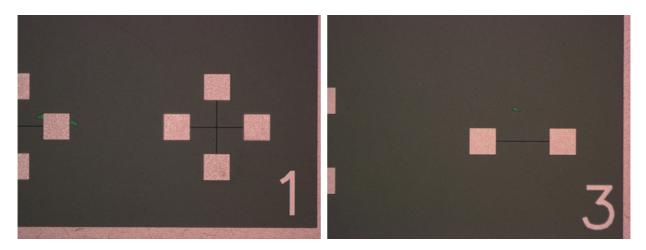

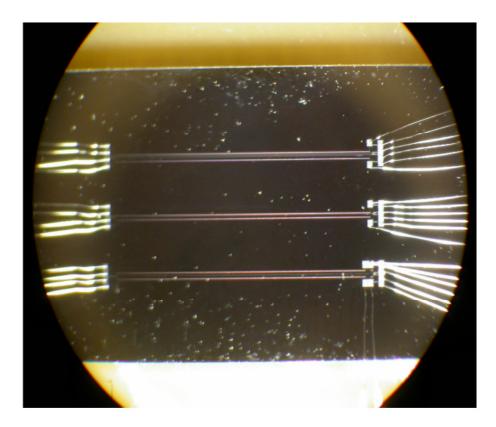

Auf den in Abbildung 27 schematisch dargestellten Wafern wurden für die weitere Charakterisierung vorwiegend Transistoren und Dioden genutzt. Beispiele solcher Strukturen zeigt die Abbildung 28. Die Transistoren und Dioden weisen unterschiedliche (Kanal-) Breiten auf, so dass unterschiedliche Anzahlen von Versetzungen charakterisiert werden konnten. Beispiele solcher Messungen zeigt die Abbildung 10 für Untersuchungen bei Raumtemperatur. Analoge Messungen erfolgten auch bei tieferen Temperaturen.

Ergebnisse einer Messungen eines Transistors bei T = 5 K sind beispielhaft in Abbildung 29 gezeigt.

Abbildung 28 Lichtoptische Abbildungen der für die Messungen verwendeten von Transistoren (links) und Dioden (rechts).

Abbildung 29 Tieftemperaturmessung eines Transistors bei T = 5 K. Der stufenweise Anstieg des Drainstromes deutet auf die Existenz von Coulomb-Blockaden hin. Die Messungen erfolgten mit Drainspannungen von 1 mV (rot) und 5 mV (blau).

## II.1.2 AP2 Funktionsnachweis Si-basierter thermoelektrischer Generatoren

Die Arbeiten im AP2 wurden vom MPI Halle koordiniert.

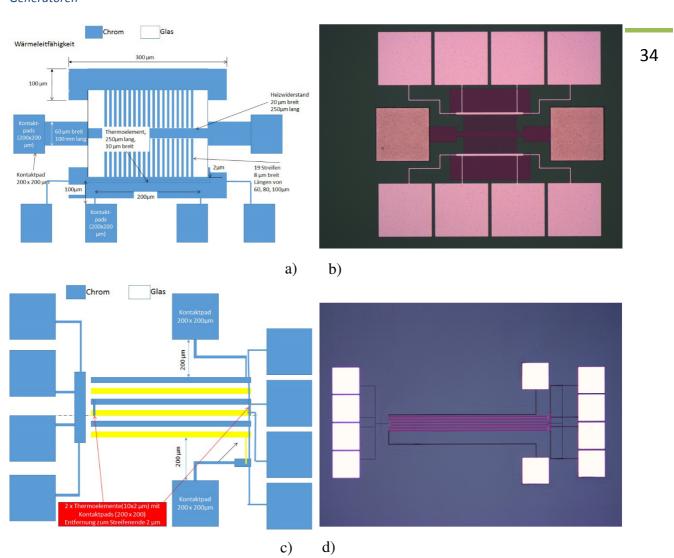

# AP 2.1 Herstellung einfacher Funktionselemente

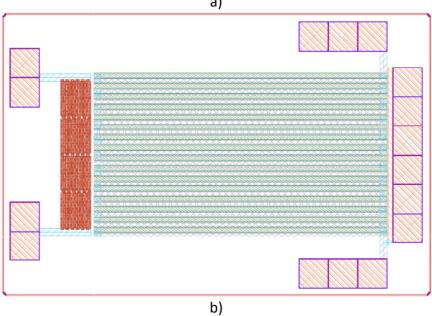

Im Projektantrag war geplant, einfache Funktionselemente zu realisieren, an denen die Funktionsfähigkeit eines Si-basierten thermoelektrischen Generators nachgewiesen werden kann. Einfache Funktionselemente (FE) bestehen aus einem oder mehreren/vielen Thermopaaren, die aus p- und n-leitenden Si-Nanostäben hergestellt sind und ein Versetzungsnetzwerk enthalten. Die Abbildung 30 zeigt Beispiele des Layouts und die lichtmikroskopischen Abbildungen solcher realisierten Funktionselemente. Funktionselemente wurden mit unterschiedlichen Anzahlen von Thermopaaren und unterschiedlichen Längen der Thermopaare hergestellt. Wie die Abbildung 30c zeigt, wurden Heizelemente sowie Thermo-

Abbildung 30 Realisierte Funktionselemente. Schema einer Struktur zur Bestimmung der Wärmeleitfähigkeit (a) und lichtmikroskopische Abbildung des realisierten Elements (b). Schema eines thermoelektrischen Generators (c) und lichtmikroskopische Abbildung der Struktur (d).

elemente integriert. Desweiteren wurden Strukturen zur Messung der Wärmeleitfähigkeit entworfen und aufgebaut (Abbildung 30a, b), mit denen die Wärmeleitfähigkeiten des nund p-leitenden Si gemessen werden können. Auch in diese Strukturen wurden Heizelemente und Thermoelemente integriert. Darüber hinaus wurden Strukturen zur Messung der elektrischen Leitfähigkeit realisiert.

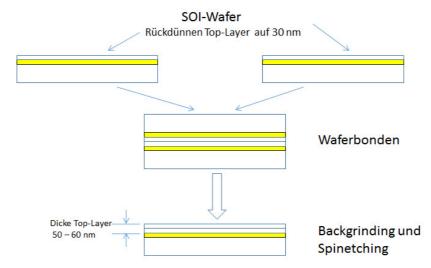

Alle Strukturen wurden jeweils auf gleichen Wafern hergestellt. Hierzu fand ein CMOS-Prozeß Anwendung. Die SOI-Ausgangswafer mit integriertem Versetzungsnetzwerk wurden durch einen Waferbondprozeß unter hydrophoben Bedingungen realisiert. Verwendung dazu fanden kommerzielle SOI-Wafer (Durchmesser 150 mm), deren Si-Schichten mittels sukzessiver thermischer Oxidation auf Dicken von ca. 30 nm rückgedünnt wurden (vergl. Abbildung 31). Daran schloß sich der Waferbondprozeß mit einer nachfolgenden Wärmebehandlung bei Temperaturen zwischen 1000°C und 1100°C. Infolge dieser Behandlung entsteht in der Grenzfläche zwischen den gebondeten Wafer ein 2-dimensionales Versetzungsnetzwerk, dessen Struktur, wie beschrieben, durch die Fehlorientierung beider Wafer modifiziert werden kann. Zum Schluß der Behandlung wird einer der Handle-Wafer durch mechanisches Schleifen (Backgrinding) und naßchemischen Ätzens (Spinetching) entfernt.

Abbildung 31 Schematische Darstellung des Herstellungsprozesses der SOI-Ausgangswafer mit integrierten Versetzungen

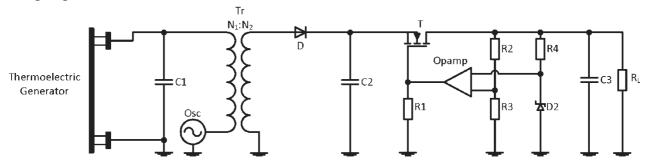

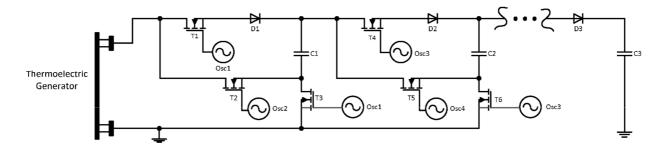

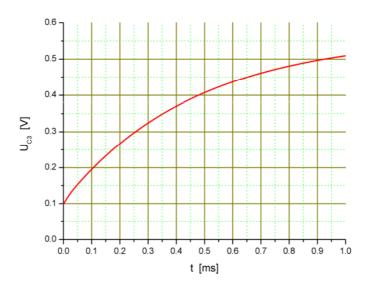

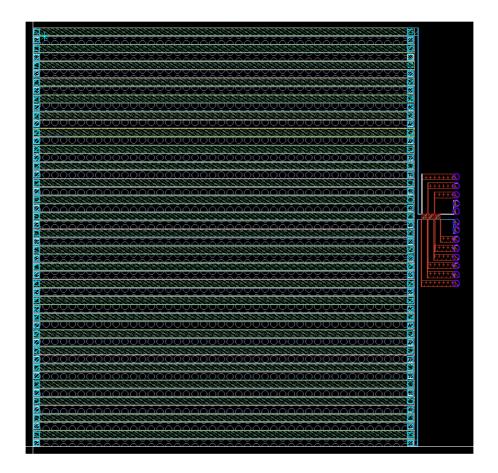

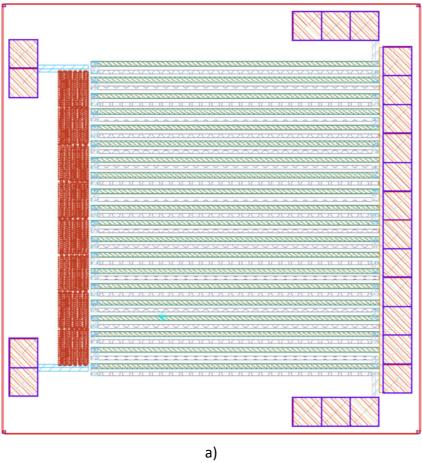

Hierdurch wird ein "neuer" SOI-Wafer mit einer Dicke der Si-Schicht von ca. 50 – 60 nm erhalten, in dessen Mitte das 2-dimensionale Versetzungsnetzwerk eingelagert ist.